ISSN: 2089-4864, DOI: 10.11591/ijres.v13.i3.pp625-642

# An active two-stage class-J power amplifier design for smart grid's 5G wireless networks

Nagisetty Sridhar, Chinnaiyan Senthilpari, Mardeni Roslee, Wong Hin Yong

Faculty of Engineering, Multimedia University, Cyberjaya, Malaysia

## **Article Info**

#### Article history:

Received Nov 30, 2023 Revised May 17, 2024 Accepted Jun 10, 2024

# Keywords:

5G Active inductor Matching networks Power amplifier Smart grid

#### **ABSTRACT**

The wireless communication networks in the smart grid's advanced metering infrastructure (AMI) applications need 5G technology to support large data transmission efficiently. As the 5G wireless communication network's overall bandwidth (BW) and efficiency depend on its power amplifier (PA), in this work, a two-stage class-J power amplifier's design methodology that operates at 3.5 GHz centre frequency by utilizing the CGH40010F model gallium nitride (GaN) transistor is presented. The proposed design methodology involves proper designing of input, output, and interstage matching networks to achieve class-J operation with improved power gain over desired BW using the advanced design system (ADS) electronic design automation (EDA) tool and estimating its integration feasibility through active element-based design approach using the Mentor Graphics EDA tool. The proposed PA provides 54% drain efficiency (D.E), 53% power added efficiency (PAE) with a small signal gain of 27 dB at 3.5 GHz and 41 dBm power output with 21 dB of improved power gain across a BW of around 400 MHz using 28 V power supply into 50  $\Omega$  load. By replacing the twostage PA's passive elements with active elements, its layout size is estimated to be  $(15.5 \times 29.2) \mu m^2$ . The results of the proposed PA exhibit its integration feasibility and suitability for the smart grid's 5G wireless networks.

This is an open access article under the <u>CC BY-SA</u> license.

625

## Corresponding Author:

Mardeni Roslee Faculty of Engineering, Multimedia University 63100 Cyberjaya, Selangor, Malaysia Email: mardeni.roslee@mmu.edu.my

## 1. INTRODUCTION

With the revolution in wireless communication technology, along with the "mobile communication sector," the "power sector" also has a significant need for upcoming 5G technology [1], especially for the smart grid's wireless communications, due to the enormous rise in the data to be transmitted. The smart grid includes communication technologies [2] and [3] that offer bidirectional data transfer in contrast to the conventional power grid for more reliable and efficient energy transmission and distribution. The advanced metering infrastructure (AMI)/smart metering applications [4] play a crucial role by enabling two-way communication for transmitting a large amount of data between the meter data management system (MDMS) of the operation centre and smart meters in the smart grid. To overcome the practical limitation in the centralized communication architecture of AMI, such as congestion or loss of data due to the rapid increase in the smart meters count and their frequent readings, a distributed architecture [5] can be used, wherein the smart meters data collected using data concentrators will be transmitted to the MDMS of the distributed operation centre using a suitable communication technology, which improves the communication architecture's efficiency and cost-effectiveness [6].

Journal homepage: http://ijres.iaescore.com

Therefore, based on the communication requirements [7] and the necessity of 5G technology in smart grid [8], the existing (3G/4G) wireless communication networks used for transmitting the data from data concentrators to the distributed operation centre can be replaced with the 5G wireless communication networks. The deployment of 5G technology will offer the reliability and desirable bandwidth (BW) to support large data transfer in the AMI applications of the smart grid. The energy consumption and BW of the 5G wireless communication networks are two important factors to consider when deploying them in AMI/smart metering applications. It is well known that a wireless communication network's BW and total energy consumption are significantly influenced by its power amplifier (PA). Therefore, choosing a PA that complies with the standards of 5G wireless communication networks utilized in the smart grid's AMI is crucial. A variety of linear mode PAs, like class-A, class-B, and class-AB with lower efficiency, and switching PAs, which deliver higher efficiency with lower linearity, like class-E and class-F described in the existing methods [9]–[15] are restricted to narrow BW and not appropriate for wideband applications. However, the class-J PA [16] has demonstrated its ability to provide good efficiency and linearity across a broad BW.

Therefore, this paper proposes a design methodology for two-stage class-J PA that operates at 3.5 GHz centre frequency by utilizing the CGH40010F model gallium nitride (GaN) transistors, which is suitable for the 5G wireless communication networks in the smart grid's AMI applications. The design model and ideology of the proposed two-stage PA focus mainly on producing output power with improved power gain along with linearity and achieving integration feasibility. The proposed design methodology involves the following key steps: choosing the transistor and its technology, analyzing its load line impedances and stability, validating the driver and power stages using load pull and spectrum analysis, validating the full stage PA design using the input matching network ((IMN), output matching network (OMN) and interstage matching network (ISMN) and estimating its integration feasibility. Following its effective design methodology, the advanced design system (ADS) and the mentor graphics electronic design automation (EDA) tools were used to run schematic and layout simulations of the proposed two-stage PA respectively.

This manuscript is organized into the following sections. Section 1 involves an overview of AMI in the 5G smart grid, the scope and objective of this manuscript, a brief methodology of the proposed PA, and its expected outcomes. Section 2 describes the existing works on class-J PAs designed for various applications with the pros and cons of the respective authors. Section 3 explains the proposed two-stage PA's design methodology in detail using a flow chart. In section 4, the results of simulated two-stage PA are presented and compared with other PA designs. The paper's conclusion is summarized in section 5 based on the simulation results obtained.

# 2. LITERATURE REVIEW

Since the introduction of class-J mode PA by Wright *et al.* [16], researchers have reported several previous studies demonstrating its potential to obtain good efficiency and linearity across a broad BW. Various class-J PA designs were reviewed and analyzed to verify their suitability for upcoming 5G wireless networks utilized in the AMI applications for the smart grid. Among these, Rezaei *et al.* [17] presented a class-J PA design using GaN technology by considering its OMN element losses. However, it has a lower power output (Pout) and efficiency compared to discrete-type PAs due to low Q and device technological constraints. Dong *et al.* [18] proposed a class-J PA design based on complementary metal oxide semiconductor (CMOS) technology with its design equations updated based on the impact of threshold voltage to analyze second harmonic losses. However, due to lower breakdown voltage restriction, CMOS-staked FET design must be employed for PA design. In [19], [20] demonstrated a class-J PA with the realization of proper half-rectified sin waveforms at the transistor gate to improve its drain efficiency (D.E) and Pout. Although these methods are useful, this PA's design and implementation are complicated due to the need for additional circuitry for higher-order filters. Hanna *et al.* [21] presented a two-stage class-J PA design with 28 GHz centre frequency using CMOS technology, which achieves good efficiency over enhanced BW and reveals its suitability for wideband 5G wireless communication applications.

Liu *et al.* [22] proposed a 5 GHz class-J PA design suitable for WLAN 802.11ax applications using GaN technology, demonstrating promising performance and commercial value. However, its performance can be further enhanced if digital pre distortion (DPD) is employed. Gao *et al.* [23] proposed a class-J PA for the 5GHz frequency band by introducing a dynamic matching network (M.N) to follow its optimum impedance trajectory for achieving maximum efficiency in the broadband and the P<sub>out</sub>. However, this dynamic M.N can be designed using active inductors (AI) to enhance its tunability. Alizadeh *et al.* [24] also proposed an active load modulation technique for an X-band class-J PA design to improve its feasibility for integration by eliminating the filter and doubler networks used in the conventional class-J2 PA. It can be noticed that there is a compromise in BW achievement as this work is focused only on improving efficiency. However, implementing a phase shifter network with an extended BW can enhance this PA's BW. Zhang *et*

al. [25] proposed a two-stage class-J PA design with a staked CMOS structure to achieve broad BW to implement in X-band. Although this PA has achieved enhanced BW, a staked structure must be employed to improve the P<sub>out</sub> due to the lower breakdown voltage of CMOS technology. Nasri et al. [26] proposed a broadband class-J PA using the Doherty structure with two CGH40010F transistors and achieved a saturated power output of 43–44.2 dBm over broadband. However, this PA design can be made feasible for integration to reduce its chip area using an active element-based design approach.

Based on this review, the existing class-J PA designs reported to date proved that they can provide a potential solution for the efficiency, linearity, and BW trade-off. However, these class-J mode PAs were designed for different applications with different technologies (GaN or CMOS) using passive elements like spiral inductors or transmission/microstrip lines to realize their M.N. The transmission lines on an integrated circuit take up a lot of space despite their simple layout and design, directly affecting the circuit's size and price. On the other hand, spiral inductors have limitations like bulky size, fixed inductance value with low Qfactor, temperature sensitivity at higher frequencies, and incompatibility with conventional CMOS technology [27]. To overcome these disadvantages, the passive lumped/spiral inductors can be replaced with AI [28], which have more advantages like inductive tuning, better Q-factor, compatibility with CMOS technology, and chip size reduction. Various wireless application circuits such as voltage-controlled oscillators (VCO), low noise amplifiers (LNA), filters, and M.Ns have been implemented using AIs [29]-[32] to achieve tunability and save the chip area and cost. Therefore, the novelty of this work involves the design of a two-stage class-J PA and an AI that achieves tunable inductance and Q-factor for replacing the passive lumped inductor of its output matching network (OMN). It also involves estimating the proposed PA's chip area using an active element-based design approach to check its feasibility for integration and suitability for smart grid AMI's 5G wireless communication networks.

#### 3. TWO-STAGE POWER AMPLIFIER DESIGN METHOD

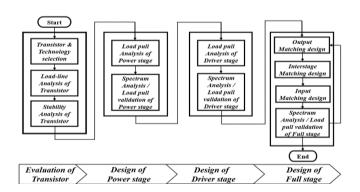

A two-stage PA is proposed with a class-J mode power stage driven by a driver stage to achieve the desired performance metrics that satisfy the 5G wireless communication network's requirements in AMI of the smart grid. As the selection of operating frequency is an important consideration in the PA design, various frequency bands such as LTE and 5G new radio (NR) [33], [34] were analyzed for their appropriate selection. Based on the analysis, a new sub-6 GHz frequency band with 3.5 GHz centre frequency, called citizen broadband radio service (CBRS) [35], was chosen as it can be appropriate for 5G wireless communications of AMI in the smart grid. Therefore, the proposed PA was initially designed with a 3.5 GHz operating frequency, and its simulations were performed with the ADS EDA tool using a 10 W GaN transistor model (CGH40010F) from CREE. The main purpose of choosing a two-stage PA topology is to get the desired P<sub>out</sub> by feeding it with lower input power. Class-A, B, AB, and C modes are often used for the driver stage design of two-stage PA. In this work class AB mode is chosen due to its low distortion compared to other modes. The step-by-step process involved in the proposed two-stage PA design methodology is described in detail with the help of the flowchart shown in Figure 1.

# 3.1. Transistor and its technology selection

As an initial step of the PA design, a GaN transistor is chosen for this work because of its high output power density, which makes it withstand high operational voltage [36] compared to gallium arsenide (GaAs) and CMOS, and they can also provide higher efficiency over wider BW. Among different GaN transistor large-signal models, a Cree's CGH40010F transistor from Wolf speed has been chosen as the main transistor because its features can provide the desired design specifications of the proposed two-stage PA.

Figure 1. Two-stage PA design flowchart

# 3.2. Bias point selection and load line analysis

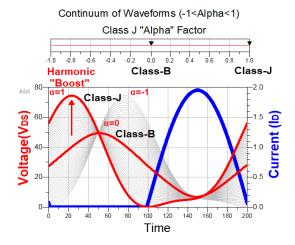

According to Wright *et al.* [16], the class-J mode operation of a transistor can be represented by its intrinsic drain voltage ( $V_{DS}$ ) with a harmonic boost and phase shift along with the half-rectified drain current ( $I_D$ ). The class-J mode  $V_{DS}$  and  $I_D$  waveforms can be obtained by presenting a complex impedance and a pure reactive impedance that can be expressed by (1) and (2) as fundamental and second harmonic loads to the selected transistor respectively, by biasing it with class-B mode.

$$Zf0 = \frac{(V_{DD} - V_{th})(1 + j\alpha)}{I_{max/2}} = R_{opt} + j\alpha R_{opt}$$

(1)

$$Z_2 f 0 = -\frac{(V_{DD} - V_{th})j\alpha}{2\left(\frac{I_{max}}{3\pi}\right)} = -\frac{j3\pi}{8} \alpha R_{opt}$$

(2)

Where the optimum resistance  $(R_{opt})$  can be represented using (3).

$$R_{opt} = 2(V_{DD} - V_{th})/I_{max} \tag{3}$$

Therefore, after selecting the transistor, the load-line analysis of the power stage was performed to obtain the class-J mode's target reference impedances. Based on this analysis, to achieve the maximum  $P_{out}$ , the selected transistor's drain is biased with a DC voltage of 28 V, which is the valid lowest  $V_{DS}$  that can be applied to allow the high swing in the drain voltage due to the harmonic boost in the class J operation mode up to its breakdown voltage of 84 V. The gate is biased with the near-threshold voltage  $(V_{th})\cong$ -3 V to initially operate the device in class-B mode to obtain the desired half-rectified  $I_D$ . The  $V_{DS}$  of class-J mode operation can be theoretically expressed as shown in (4).

$$V_I(\theta) = V_{dc}(1 + \sin\theta)(1 + \alpha\cos\theta) \tag{4}$$

The "Alpha" factor ( $\alpha$ ), as shown in (4), can be varied from -1 to 1, and each  $V_{DS}$  waveform for different values of  $\alpha$  results in the same theoretical efficiency when combined with half rectified  $I_D$ , causing the class-J mode to expand its BW.

For  $\alpha=1$ , (4) can be expanded as shown in (5).

$$V_J(\theta) = V_{dc}(1 + \sin\theta + \cos\theta + \frac{1}{2}\sin 2\theta)$$

(5)

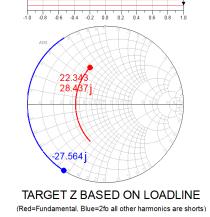

Therefore, when ( $\alpha$ ) is moved from "0" (i.e., class-B mode) to "1" on the slider, a harmonic boost and a phase shift can be noticed in  $V_{DS}$  due to the  $sin2\theta$  and  $cos\theta$  terms of (5) respectively, which resemble the class-J mode's  $V_{DS}$  and  $I_D$  waveforms as shown in Figure 2. The target reference load impedances corresponding to the class-J mode operation (for  $\alpha$ =1), which are obtained from load line analysis using (1) and (2) are represented in Figure 3 using a Smith chart.

Figure 2. Class-B to J operation mode w.r.t α=0 to 1 Figure 3. Target reference load impedances of class-J operation mode

Unlike the power stage, the driver stage drains and the gate bias voltages are set as 28 and -2.7 V, respectively, for the corresponding class-AB mode, and its target reference impedances are obtained directly from the CGH40010F device datasheet as 3.18-j\*13.3 and 14.6+j\*7.45. The selection of target reference impedances is verified by performing load line analysis using design equations in the ADS workspace.

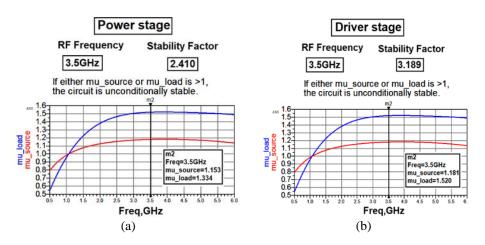

## 3.3. Stability analysis

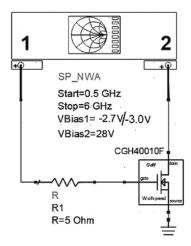

Once the power stage (class-J) and driver (class-AB) stage transistors are biased, their stability analysis was performed corresponding to the respective biasing points for a frequency range of (3-4) GHz using S-parameter network analyzer (SP\_NWA) as shown in Figure 4. The unconditional stability of the transistors in the PA can be assured by satisfying two main conditions such as the Rollet stability factor (K) expressed in (6) must be greater than unity (i.e., K>1), and the stability measure (b) expressed in (7) must be a positive value (i.e.,>0).

$$K = \frac{\left\{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11*}S_{22} - S_{12*}S_{21}|^2\right\}}{\left\{2 * |S_{12*}S_{21}|\right\}} \tag{6}$$

$$b = \{1 + |S_{11}|^2 - |S_{22}|^2 - |S_{11*}S_{22} - S_{12*}S_{21}|^2\}$$

(7)

In this work, a stabilization resistor of 5  $\Omega$  is connected with the transistor's gate terminal in series to ensure the transistor's unconditional stability by making (K>1) and (b>0) over a desired frequency range.

Figure 4. Stability analysis of a GaN transistor for driver and power stage

# 3.4. Load pull analysis

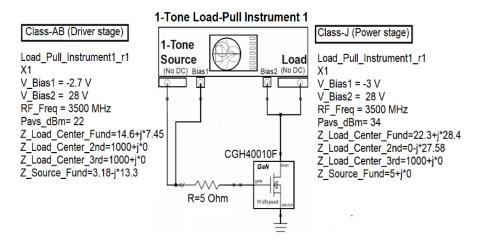

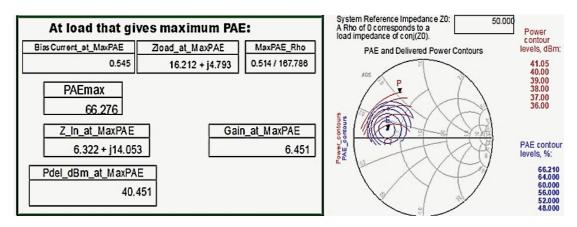

After ensuring the unconditional stability of the driver and power stage's transistors, their corresponding load-pull simulations were performed to get the optimum source  $(Z_S)$  and load  $(Z_L)$  impedances corresponding to the maximum power added efficiency (PAE) and the  $P_{out}$ . These  $Z_S$  and  $Z_L$  values obtained using load-pull analysis will be used for M.N's design. Load pull simulations can be performed on a large signal model of the GaN transistor (CGH40010F) using the harmonic balance (HB) 1-Tone load pull design guide in the ADS EDA tool. Initially, the transistor's fundamental source and load impedance values for power and driver stages obtained from load line analysis and device data sheet respectively are used as target reference impedances in the HB1-Tone load pull simulation setup, as shown in Figure 5.

The second harmonic of the driver stage was set at high impedance to keep it as an open circuit, wherein the power stage, the second harmonic impedance obtained from load line analysis, is used as the target reference impedance. The third harmonic impedance of the driver and power stages were set at high impedance to keep it as an open circuit, and other harmonics were terminated at 50  $\Omega$ . The fundamental and second harmonic load impedances at of power stage are crucial to obtaining the desired class-J operation with enhanced BW. The driver (class-AB) and power (class-J) stages with respective biasing voltages and input powers at 3.5 GHz RF frequency are validated by placing these  $Z_S$  and  $Z_L$  values at their corresponding transistor's terminals instead of their 50  $\Omega$  terminations.

630 ☐ ISSN: 2089-4864

Figure 5. Load-pull analysis on the stabilized transistor for driver and power stage modes

# 3.5. IMN, OMN, and ISMN design

The next important step after validation of  $Z_S$  and  $Z_L$  is the design of appropriate M.Ns. Proper design of impedance M.Ns can improve the efficiency and BW of the proposed PA by mitigating the errors due to second-order effects. In general, harmonic distortion and intermodulation distortion are the crucial second-order effects that can affect the operation of the GaN transistor when a one-tone signal feeds the PA. The PA design should be optimized for low output impedance and high linearity to mitigate these harmonic and intermodulation distortions. By providing the proper impedance transformation between the source, transistor's terminals, and load, the M.Ns can minimize the reflections and improve power transfer efficiency, reducing harmonic and intermodulation distortion caused by impedance mismatch and improving overall performance. Proper M.Ns design also reduces the errors caused by the instability due to second-order effects such as variations in parasitic capacitances and can extend the usable BW.

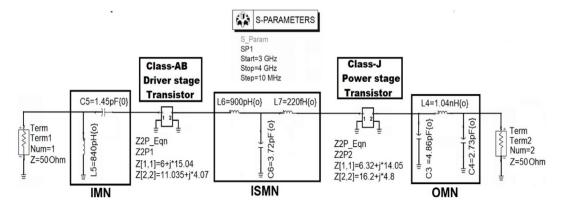

Therefore, initially, to achieve approximately 500 MHz BW with 3.5 GHz centre frequency, 3 lumped element-based L,  $\pi$ , and T-type M.Ns were designed for corresponding IMN, OMN, and ISMN, because of the proposed PA's two-stage structure. The values of passive lumped inductors and capacitors in these L,  $\pi$ , and T-type M.Ns were calculated using their general design equations in terms of Q-factor. To validate the proper design of the M.Ns, the driver and power stage transistors are represented as "Z2P\_Eqn" blocks by placing the optimum impedances  $Z_S$  and  $Z_L$  as Z [1,1], Z [2,2], and the S-parameters were measured for a desired frequency range of (3-4) GHz using the S-parameter sweep setup of the ADS EDA tool as shown in Figure 6. The transfer impedances of transistors ((i.e., Z [1,2] and Z [2,1]) are ignored, because the M.Ns will be designed to match only these Z [1,1] and Z [2,2]) of driver and power stage transistors with each other and also with the corresponding source and load terminations. In this work, as the GaN transistor is used in the class-J power stage as the active device, the second-order effects are taken care of by its drain-source capacitor (Cds), and the capacitor C3 of OMN as their values are considered as short circuit at higher harmonic frequencies.

Figure 6. IMN, OMN, and ISMN with S-parameter sweep setup

## 3.6. Validation of proposed two-stage power amplifier

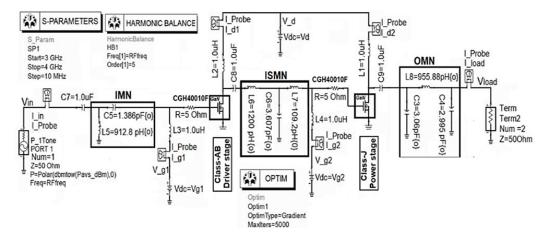

The proposed two-stage PA with 50  $\Omega$  terminations is validated by placing these designed passive lumped element-based M.Ns at the appropriate places, as shown in Figure 7, and optimizing them using the ADS optimization tool to get the desired performance. The passive lumped element-based M.Ns were initially realized to validate the proposed PA. Its simulated VDS and ID waveforms were observed to verify the standard class-J PA operating mode of the proposed PA's power stage. The validation of the proposed PA can be done by measuring its performance parameters such as  $P_{out}$ , gain, BW, D.E, and PAE using the HB simulator in the ADS tool when it is fed by input power (Pavs\_dBm) of 20 dBm with 3.5 GHz operating frequency. After validation of the proposed two-stage PA design with passive lumped elements, its final layout design can be realized by replacing its ideal passive lumped elements with active elements (transistors) to check its feasibility for integration.

Figure 7. Proposed two-stage class-J PA's schematic circuit

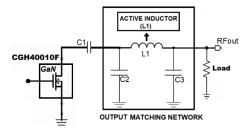

## 3.7. Active inductor design

The proposed PA design was intended to replace its passive lumped elements with active elements to make it feasible for integration. Therefore, after validating the proposed PA design with passive lumped element-based M.Ns, as an initial step, an AI is designed to replace the passive lumped inductor in its OMN, as shown in Figure 8. The AI design allows us to overcome the disadvantages of commonly used spiral inductors [28] and achieves tunable inductance with reduced chip area.

Figure 8. AI-based OMN for class-J PA

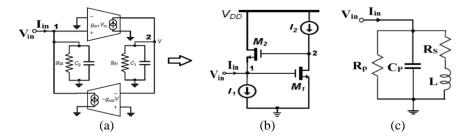

Therefore, after validating the proposed two-stage PA with lumped element-based M.Ns, as shown in Figure 7, different gyrator-C-based AI designs were reviewed and analyzed to replace its OMN's passive lumped inductor with AI. Based on the theory of gyrator-C topology, when two transconductors are connected back-to-back, it can be termed a gyrator. When a capacitor is connected to a gyrator's output, its equivalent input impedance can be synthesized as an inductor and termed gyrator-C- AI, as shown in Figure 9. Its basic topology can be represented in terms of transconductors as shown in Figure 9(a). By replacing the gyrator-C AI's transconductors with common drain and common source configured transistors (MOSFETs), respectively, as shown in Figure 9(b), its inductance along with the parasitic parameters can be depicted as shown in Figure 9(c) using an RLC equivalent circuit.

Figure 9. Gyrator-C AI (a) basic topology, (b) MOSFET-based topology, and (c) equivalent RLC circuit

The inductance (L) of the MOSFET-based gyrator-C AI, along with parasitic resistances  $(R_P, R_S)$  and capacitance  $(C_P)$ , can be realized from its admittance (Y) expression as shown in (8) that is obtained by applying KCL at nodes 1 and 2.

$$Y = \frac{I_{in}}{V_{in}} = SC_{gs1} + g_{m1} + \frac{1}{S\left(\frac{C_{gs2}}{G_{m1}G_{m2}}\right) + \left(\frac{g_{ds1}}{G_{m1}G_{m2}}\right)}$$

(8)

This admittance (Y) expression of the gyrator-C AI shown in (8) is analogous to the admittance (Y) expression of its RLC equivalent circuit as shown in Figure 9(c), and it can be expressed as shown in (9).

$$Y = \frac{I_{in}}{V_{in}} = SC_P + \frac{1}{R_P} + \frac{1}{S(L) + (R_S)}$$

(9)

By comparing (8) and (9) the L of the MOSFET-based gyrator-C AI along with the equivalent RLC circuit parameters  $(R_P, R_S)$  and  $(C_P)$  are expressed in terms of the transistor's transconductances and internal capacitances as shown in (10).

$$L = \frac{c_{gs2}}{g_{m1}g_{m2}}, R_s = \frac{g_{ds1}}{g_{m1}g_{m2}}, R_P = \frac{1}{g_{m1}}, C_p = C_{gs1}$$

(10)

The input impedance  $(Z_{in})$  of the gyrator-C AI can be expressed as the inverse of Y in terms of equivalent RLC circuit parameters L,  $R_P$ ,  $R_S$ , and  $(C_P)$  as shown in (11).

$$Z_{in} = \frac{1}{Y} = \left(\frac{R_S}{C_p L}\right) \frac{S \frac{L}{R_S} + 1}{S^2 + S\left(\frac{1}{R_p C_p} + \frac{R_S}{L}\right) + \left\{\frac{R_p + R_S}{R_p C_p L}\right\} = \{\omega_0^2\}}$$

(11)

From (11), the self-resonating frequency ( $\omega 0$ ) of this MOSFET-based gyrator-C AI when  $R_P >> R_S$  is expressed as shown in (12).

$$\omega 0 = \sqrt{\frac{R_p + R_s}{R_p c_p L}} = \sqrt{\frac{1}{c_p L}} = \sqrt{\frac{g_{m_1} g_{m_2}}{c_{g_{s_1}} c_{g_{s_2}}}}$$

(12)

The inductive frequency range of this gyrator-C AI can be  $(\omega z > \omega > \omega 0)$  where  $\omega z$  is a lower bounded frequency that can be expressed as shown in (13).

$$\omega z = \frac{R_S}{L} = \frac{g_{ds1}}{c_{gs2}} \tag{13}$$

This MOSFET-based gyrator-C AI's quality (Q) factor at  $\omega = \omega 0$  can be obtained from  $Z_{in}$  expression in terms of the transistor's transconductances and internal capacitances, as shown in (14).

$$Q(\omega 0) = \frac{Im[Z_{in}]}{Re[Z_{in}]} \cong \frac{\omega_0 L}{R_S} = \frac{1}{g_{ds1}} \sqrt{\frac{g_{m1}g_{m2}c_{gs2}}{c_{gs1}}}$$

(14)

From the expressions of the L and Q factor of MOSFET-based gyrator-C AI, it can be noticed that varying the widths of the transistors ( $M_1$  and  $M_2$ ) varies their transconductances and internal gate capacitances at the same time, due to which it is difficult to tune the L and Q factor independently.

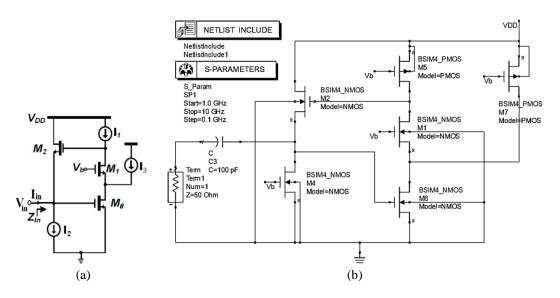

Based on this analysis, in this work, an AI is designed using the Weng-Kuo cascode topology [31] for achieving a 1 nH inductance value at 3.5 GHz centre frequency for replacing the passive lumped inductor in OMN of the proposed PA. The main reason for choosing this topology is its ability to tune the L and Q factor independently which can be achieved by adding a MOSFET (M<sub>1</sub>) in cascode to the main MOSFET of the basic MOSFET-based gyrator-C AI structure as shown in Figure 10(a). With this configuration, independent tuning of L and Q factors is possible because  $g_{m6}$  is proportional to  $I_1$ - $I_3$  while  $g_{m1}$  is only proportional to  $I_1$ . In addition, this topology benefits from less chip area and low power consumption compared to the passive lumped or spiral inductor during its integration.

Similar to the basic gyrator -C AI's RLC equivalent circuit parameters, this AI's equivalent circuit parameters that are obtained from its  $Z_{in}$  expression can be represented in terms of transconductances and parasitic capacitances of MOSFETs 1.2 and 6 as shown in (15):

$$L = \frac{c_{gs2}}{g_{m6}g_{m2}}, R_s = \frac{g_{ds6}g_{ds1}}{g_{m6}g_{m2}g_{m1}}, R_p = \frac{1}{g_{ds2} + g_{m1} \approx g_{m1}}, C_p = C_{gs6}$$

(15)

the resonant frequency and corresponding Q-factor can be represented as shown in (16) and (17).

$$\omega 0 = \sqrt{\frac{g_{m6}g_{m2}}{c_{gs1}c_{gs2}}} \tag{16}$$

$$Q(\omega 0) = \frac{\omega_0 L}{R_S} = \frac{g_{m_1}}{g_{ds6} g_{ds1}} \sqrt{\frac{g_{m6} g_{m2} c_{gs2}}{c_{gs1}}}$$

(17)

Therefore, an AI based on cascode topology as shown in Figure 10 is simulated with a gate bias (Vb)=1.5 V and a supply voltage (VDD)=3.3 V to obtain desired L and Q factor values, and the ideal current sources  $I_1$ ,  $I_2$  and  $I_3$  in its topology as shown in Figure 10(a) are replaced with saturated MOSFETS M5, M4, and M7 as shown in Figure 10(b). The MOSFETs  $M_1$ ,  $M_2$ ,  $M_4$ ,  $M_5$ ,  $M_6$ , and  $M_7$  W/L ratios of the AI are tuned and optimized for achieving a tunable inductance value of 1 nH $\approx$ 956 pH (i.e., the passive lumped inductor's inductance value in OMN) at the 3.5 GHz centre frequency using S-parameter simulator.

Figure 10. Cascode AI (a) topology and (b) schematic simulation in ADS

#### 4. RESULTS AND DISCUSSION

The simulation results of proposed two-stage class J PAs are presented in the order of their design methodology steps. The proposed PA and the AI of its OMN are validated by evaluating their performance parameters. Finally, the integration feasibility and suitability of the proposed two-stage class-J PA for 5G wireless communication networks in smart grid's AMI are verified by performing its layout simulations with an active element-based design approach using the Silterra  $0.13~\mu m$  process in MG EDA tool. The simulation results of all desired performance metrics of the proposed PA and the AI of its OMN are described as follows.

#### 4.1. Stability

The simulation results of the stability analysis performed, as shown in Figure 4, reveal that the active device (i.e., GaN transistor) is unstable without any stabilization resistance as its stability factor (K) is <1. However, with the placement of a series resistance at the gate of the transistor, the stability factor analysis is represented in Figure 11. It is observed from Figure 11(a) and Figure 11(b) that the K becomes >1 and the stability measure is >0 over the desired frequency range (3-4) GHz which ensures the unconditional stability of the power and driver stage transistors.

Figure 11. Stability factor analysis (a) power stage and (b) driver stage

## 4.2. Optimum input /source and output/load impedances from load pull

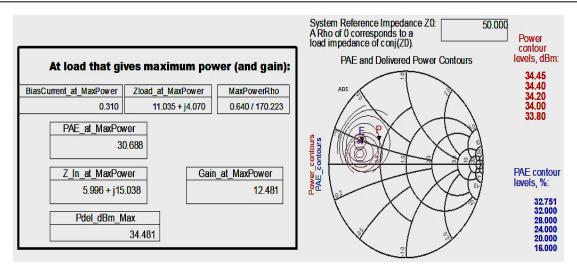

The simulator will measure the  $P_{out}$  and PAE from the load pull analysis and generate their contour plot for every swept point. Figure 12 shows the load pull simulation results where the optimum  $Z_S$  and  $Z_L$  of the power stage transistor obtained corresponding to maximum PAE are 6.322+j\*14.053 and 16.212+j\*4.793, respectively. Similarly, Figure 13 shows the optimum  $Z_S$  and  $Z_L$  of the driver stage transistor obtained corresponding to the maximum  $P_{out}/gain$  are 5.996+j\*15.038 and 11.035+j\*4.070, respectively. The values of  $Z_S$  and  $Z_L$  obtained from the simulation results of power and the driver stage's load-pull analysis corresponding to the maximum PAE and maximum power are shown in Table 1.

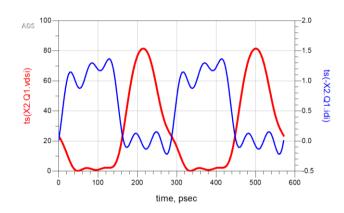

By presenting these optimum impedances at respective transistor terminals, the power and driver stages of the proposed two-stage PA are validated by computing their performance parameters using equations with the help of the "MeasEqn" component of the HB simulator in the ADS EDA tool respectively. From the validation of the power stage, it is observed that there is a harmonic boost in intrinsic drain voltage time domain signal (ts(X2.Q1.vdsi)) approximately up to 3 times (i.e.,  $\approx$ 84 V) of the supplied drain voltage of 28 V and a phase shift that reduces its overlap with half rectified drain current time domain signal (ts(X2.Q1.idi)) as shown in Figure 14, which resembles the  $V_{DS}$  and  $I_{D}$  waveforms of class-J operation mode.

Figure 12. Optimum Z<sub>S</sub> and Z<sub>L</sub> of the power stage transistor w.r.t maximum PAE

Figure 13. Optimum Z<sub>S</sub> and Z<sub>L</sub> of driver stage transistor w.r.t maximum power and gain

| Table 1 | . Zs and | 7 abs  | lo and | faces | 4ha 1 | المحما  | 11    | 1     |

|---------|----------|--------|--------|-------|-------|---------|-------|-------|

| rame i  | . Zs and | ZI ODI | lamed  | пош   | me    | ioau-bu | n ana | IVSIS |

| Stage  | Optimum impedance | Load pull analysis | Max PAE (%) | Max power (dBm) |  |  |  |

|--------|-------------------|--------------------|-------------|-----------------|--|--|--|

| Power  | Source            | 6.32+j*14.0        | @66         | 40.5            |  |  |  |

|        | Load              | 16.2+j*4.8         |             |                 |  |  |  |

| Driver | Source            | 6.0+j*15.0         | 31          | @34.5           |  |  |  |

|        | Load              | 11.0+j*4.0         |             |                 |  |  |  |

Figure 14. Intrinsic V<sub>DS</sub> and I<sub>D</sub> of power stage (class-J) transistor

## 4.3. Output power and efficiency

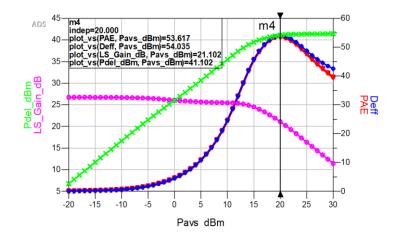

It is observed that by feeding the power stage (class-J) of the proposed PA with 34 dBm input power at 3.5 GHz centre frequency, its PAE, and D.E are estimated as 60.5% and 73.4%, and the P<sub>out</sub> is estimated as 41.5 dBm with 7.5 dB power gain. Similarly, the driver stage delivers 34.9 dBm P<sub>out</sub> with 12.9 dB power gain by feeding it with 22 dBm input power at 3.5 GHz centre frequency. Finally, by driving the class-J power stage with the class-AB driver stage using proper M.Ns design as shown in Figure 7, the proposed PA delivers 41.1 dBm P<sub>out</sub> with 21.1 dB improved power gain, 54% D.E and 53% PAE using the reduced input power/ available source power (Pavs\_dBm) of 20 dBm due to its two-stage structure. These performance parameters are tabulated as shown in Table 2.

Table 2. Performance parameters of two-stage PA

| rable 2. I chormance parameters of two stage 171 |           |              |                        |         |         |  |  |

|--------------------------------------------------|-----------|--------------|------------------------|---------|---------|--|--|

| Stage                                            | Pin (dBm) | LS_Gain (dB) | P <sub>out</sub> (dBm) | PAE (%) | D.E (%) |  |  |

| Power (without M.Ns)                             | 34        | 7.5          | 41.5                   | 60.5    | 73.4    |  |  |

| Driver (without M.Ns)                            | 22        | 12.9         | 34.9                   | 32      | 33      |  |  |

| Two-stage (with M.Ns)                            | 20        | 21.1         | 41.1                   | 53      | 54      |  |  |

636 ☐ ISSN: 2089-4864

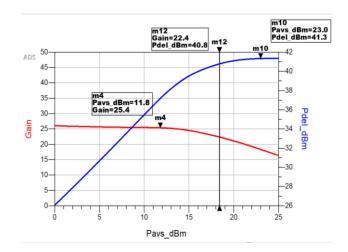

# 4.4. Performance over input power sweep

The variations of these performance parameters by sweeping the (Pavs\_dBm) of the PA using the HB simulator are shown in Figure 15. These simulation results reveal that 54% D.E, 53% PAE as their maximum values, and 41 dBm  $P_{out}$  with 21 dB power gain were obtained for corresponding Pavs\_dBm of 20 dBm. This improvement in the proposed two-stage PA's power gain is obtained at the cost of reducing its D.E and PAE. In general, the PAE and D.E of a GaN PA will not have the same values as they measure different aspects of the PA. However, the PAE and D.E of the proposed PA are close to each other because the load pull simulations of the proposed PA were performed to obtain optimum  $Z_L$  corresponding to maximum PAE, and it was initially designed using low-loss passive components and high-efficiency GaN transistor, resulting in minimal losses. The performance metrics of the proposed PA demonstrate its ability to achieve the desired  $P_{out}$  with improved power gain and linearity.

Figure 15. Two-stage PA's performance parameters w.r.t Pavs dBm sweep

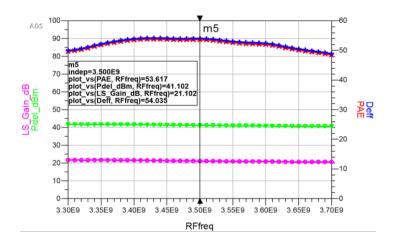

# 4.5. Bandwidth

Similarly, the variation of the proposed two-stage PA's performance parameters Vs RF frequency was measured using an HB simulator, and the respective simulation results reveal that D.E of 54%, PAE of 53% at 3.5 GHz centre frequency, and 41 dBm P<sub>out</sub> with approximately 21 dB power gain is maintained across 400 MHz BW (i.e., 3.3 to 3.7 GHz) were obtained as shown in Figure 16. This enhanced BW demonstrates the proposed PA's ability to maintain its P<sub>out</sub> and power gain across a wide frequency range and shows its suitability for next-generation 5G wireless networks of smart grid's AMI applications.

Figure 16. Two-stage PA's performance parameters w.r.t RF frequency

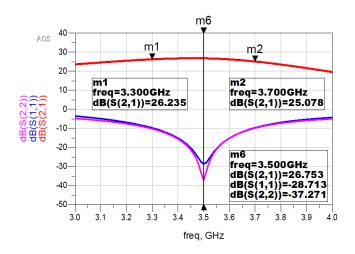

#### 4.6. S-Parameters

The proper design of impedance-M.Ns of the optimized two-stage PA can be validated by measuring its S-parameters such as input, output reflection coefficients S (1,1), S (2,2), and small-signal gain S (2,1) using an S-parameter simulator of ADS EDA tool to ensure its improved interference resistance. It can be noticed that a small signal gain S (2,1) above 25 dB over 400 MHz BW (i.e., 3.3 to 3.7 MHz) with a maximum value of approximately 27 dB along with S (1,1), S (2,2)>-25 dB at 3.5 GHz centre frequency were obtained shown in Figure 17. These S-parameters ensure that the M.Ns are designed properly as the reflections are reduced which can reduce the impact of interference.

Figure 17. The proposed two-stage class AB/J PA's S-parameters

## 4.7. Issues of system interference resistance and error rate

Interference in a GaN PA refers to any unwanted signals that interfere with the proper operation of the PA, which can cause degradation in its performance. The various sources of interference, including other RF signals, electromagnetic interference (EMI), or thermal interference, can affect the performance and reliability of PA by introducing harmonic distortions into the output signal, leading the PAs to nonlinear behaviour. Therefore, improving the interference resistance while designing a PA is important to maintain its performance in the presence of external interference. In this work, the interference resistance of the proposed PA can be improved to mitigate the effects of interference by designing proper input/output impedance M.Ns, which can help to reduce reflections and distortions and improve the efficiency and linearity of the PA, which can help reduce the impact of interference.

On the other hand, the error rate of a PA refers to the frequency and severity of errors or distortions introduced into its output signal. The error rate can be measured in terms of bit error rate, adjacent channel power ratio, and error vector magnitude. The error rate of a GaN PA can be high due to various factors, such as input power levels, load impedance, operating frequency, and circuit design. In this work, the proposed PA's design is optimized to reduce distortions with proper impedance M.Ns that help achieve good linearity, reducing the error rate. Therefore, the improved interference resistance and reduced error rate of the proposed PA are assured by validating the M.Ns design through S-parameters and linearity measurements.

## 4.8. Linearity

In addition to the parameters such as DE, PAE, and BW of the PA, its linearity is also a crucial measure for performance evaluation. The linearity of a PA can be defined as a measure of how the PA produces an output that is a scaled version of the input signal without any distortion or nonlinear effects. The linearity of the PA may generally be evaluated using metrics like P1dB/P3dB (1 dB/3 dB compression point), third-order intercept point, AM-PM distortion, and adjacent channel power ratio, depending on its RF input signal and transistor technology used.

In this work, the proposed PA's linearity is evaluated using a 3 dB compression point as it is initially designed using a GaN transistor and fed by a continuous wave (CW)/1-tone signal as its RF input. The 3 dB compression point is defined as the point at which the gain of the PA begins to compress due to nonlinearity, and the output power no longer increases linearly with the input power. According to the simulation findings, the gain of the proposed PA is compressed by 3 dB (from 25.4 dB to 22.4 dB), as shown

638 □ ISSN: 2089-4864

in Figure 18. At this 3 dB compression point, the  $P_{out}$  value is 41 dBm, which is nearly as high as the saturated power ( $P_{sat}$ ) value (i.e., 41.3 dB), which reveals that the proposed PA's linearity is good, reducing its error rate.

Figure 18. Linearity measurement using 3 dB compression point

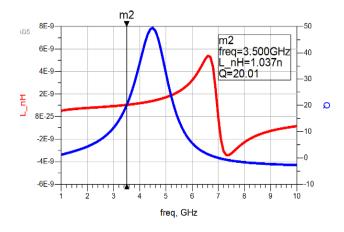

#### 4.9. Q factor and L of AI

After validation of lumped element-based two-stage PA's simulation results, the AI's schematic simulation was performed as shown in Figure 10(b), and by tuning the widths of MOSFETs in the AI an inductance value of 1 nH with a Q factor of 20 at 3.5 GHz was obtained, as shown in Figure 19. As this inductance value is almost equal to the value of the passive lumped inductor in the OMN of the proposed PA, it can be replaced with this AI to achieve tunability, reduced chip area, and less power consumption.

Figure 19. Q-factor and L of AI (vs) frequency

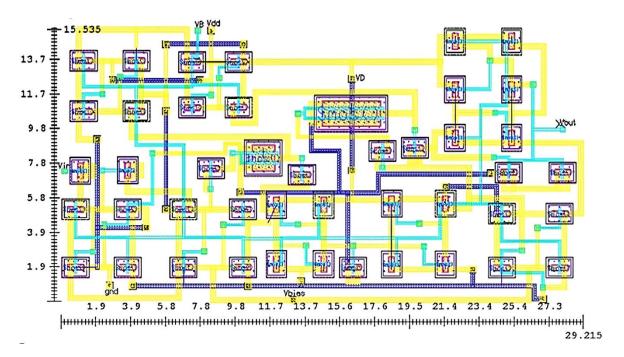

# 4.10. Proposed PA's layout design

Therefore, after validating the proposed two-stage PA's performance with lumped-element based M.Ns design, the layout design was performed to assess its integration feasibility and chip size. As the proposed PA of this work was initially designed using passive lumped elements, its final layout design is realized by replacing all of them with active elements such as the AI of OMN. The proposed PA's active element-based layout design was performed using the mentor graphics EDA tool. Since the load pull simulations cannot be performed using this tool, the  $R_{opt}$  values of the driver and power stages obtained using the ADS tool were taken as reference values. To get these reference  $R_{opt}$  values, the I<sub>D</sub> of chosen Silterra Nmos transistors in the mentor graphics EDA tool were tuned by changing their aspect ratios.

Finally, by replacing all the elements in the proposed two-stage PA with Silterra 130 nm transistors and optimizing them as closely as possible, the chip size of its layout design shown in Figure 20 is estimated as  $(15.5 \times 29.2) \, \mu m^2$ .

Figure 20. The proposed two-stage PA's active element-based core layout

# 4.11. Performance comparison

The proposed two-stage PA's performance parameters were compared with similar PAs in the literature, as shown in Table 3. The following are the noteworthy points by comparing the proposed PA's performance with recent similar PAs that were designed with different operating frequencies and technologies. A 5 GHz class-J PA design [22] suitable for WLAN 802.11ax applications using GaN technology delivers 55% maximum PAE and 38 dBm  $P_{out}$ , whereas the proposed PA delivers 41 dBm of max  $P_{out}$  with 2-stage structure. However, this PA's power gain is comparatively higher than the proposed PA due to its 3-stage structure. A dynamic M.N-based class-J PA design [23] that operates at a 5G frequency band delivers a  $P_{sat}$  of 39.8 dBm and a maximum PAE of 50.6%. Our class-J PA delivers a maximum PAE of 53% with a max  $P_{out}$  of 41 dBm using the same GaN transistor with lower input power. However, the performance of PA can be further improved using an AI-based OMN structure.

A class-J PA with the 2-stage structure design using an active load modulation technique for the X-band presented in [24] eliminates the class-J2 PA's filter and doubler networks to improve its feasibility for integration. It delivers 50% PAE using an auxiliary circuit for phase-shifting that may require additional space. Whereas our proposed PA of this work delivers a PAE of 53% using a similar 2-stage structure without any auxiliary network for phase-shifting. A two-stage class-J PA design with a staked CMOS structure [25] delivers a max P<sub>out</sub> of 20.2 dBm with 15 dB power gain and 29.7% PAE. Using a similar 2-stage structure, the PA of this work based on a GaN transistor delivers a max P<sub>out</sub> of 41 dBm with 21 dB power gain and 53% PAE without any stacked structure due to its high-power handling capability. Using the Doherty structure, a broadband class-J PA presented in [26] achieved a saturated power output of 43–44.2 dBm and a small signal gain of 10–13 dB. In comparison, using a two-stage structure, our class-J PA provides a max P<sub>out</sub> of 41 dBm with 21 dB power gain and a small signal gain of approximately 26 dB with the same number of transistors.

Moreover, the class-J PA designs in literature utilized transmission/microstrip lines or spiral inductors for realizing their M.Ns, which leads to large chip areas and high-power consumption. Compared to these existing class-J PA designs, the unique contribution of the proposed two-stage class-J PA is its active element-based layout design approach using AI for its OMN, which exhibits its feasibility for very large scale integration (VLSI) integration. In addition, the design methodology of proposed PA demonstrates its

640 ☐ ISSN: 2089-4864

potential for enhancing wireless communication capabilities in embedded, reconfigurable systems within the smart grid.

Table 3. Performance comparison

| Ref./Parameters            | [22] 2018 | [23] 2020 | [24] 2020  | [25] 2021 | [26] 2022 | This work |

|----------------------------|-----------|-----------|------------|-----------|-----------|-----------|

| Technology                 | GaN       | GaN       | GaAs       | CMOS      | GaN       | GaN       |

| Frequency [GHz]            | 5         | 3.7       | 10         | 9.5       | 3.5       | 3.5       |

| BW [GHz]                   | 4.9-5.9   | 3.3-4.2   | 9.1 - 10.8 | 8.7-11.8  | 3.0-3.7   | 3.3 - 3.7 |

| Max P <sub>out</sub> [dBm] | 37.7      | 39.8      | 29         | 20        | 44.2      | 41        |

| Max gain [dB]              | 31.7      | -         | 12         | 15        | 13        | 21        |

| Max PAE [%]                | 54.6      | 50.6      | 50         | 29.7      | -         | 53        |

| Max D.E [%]                | -         | -         | 71         | -         | 74        | 54        |

#### 5. CONCLUSION

This work presents a class-J PA with a two-stage structure, suitable for upcoming 5G wireless networks used in the smart grid's AMI applications. The proposed PA was designed with a 3.5 GHz operating frequency (i.e., sub-6 GHz 5G frequency) using lumped element-based M.Ns based on a two-stage PA design flow chart, and its simulations were performed using the ADS EDA tool. Its simulation results demonstrate that the proposed two-stage PA delivers 54% D.E, 53% PAE at 3.5 GHz centre frequency with 27 dB small signal gain and 41 dBm P<sub>out</sub> with approximately 21 dB of improved power gain over a 400 MHz BW (i.e., 3.3 to 3.7 GHz).

Although the proposed two-stage PA with lumped element-based M.Ns exhibits good performance parameters, its overall size can be reduced to make it feasible for integration by replacing its passive lumped elements with active element designs. Therefore, as an initial step, an AI based on the Weng-Kuo cascode topology is designed and simulated to replace the passive lumped inductor in OMN of the proposed PA. In addition, by replacing its other passive lumped elements with active elements, the proposed PA layout's chip size is estimated as  $(15.5 \times 29.2) \ \mu m^2$ , indicating its integration feasibility. However, there is scope for enhancing the proposed PA's performance with improved active-element-based designs to make it more appropriate for (sub-6 GHz) AMI/smart metering applications of 5G smart grid.

## REFERENCES

- [1] T. M. Ho *et al.*, "Next-generation wireless solutions for the smart factory, smart vehicles, the smart grid and smart cities," *arXiv: Signal Processing*, 2019, doi: 10.48550/ARXIV.1907.10102.

- [2] Y. Yan, Y. Qian, H. Sharif and D. Tipper, "A survey on smart grid communication infrastructures: motivations, requirements and challenges," *IEEE Communications Surveys & Tutorials*, vol. 15, no. 1, pp. 5-20, 2013, doi: 10.1109/SURV.2012.021312.00034.

- [3] F. E. Abrahamsen, Y. Ai, and M. Cheffena, "Communication technologies for smart grid: a comprehensive survey," *Sensors*, vol. 21, no. 23, p. 8087, Dec. 2021, doi: 10.3390/s21238087.

- [4] R. R. Mohassel, A. Fung, F. Mohammadi, and K. Raahemifar, "A survey on advanced metering infrastructure," *International Journal of Electrical Power & Energy Systems*, vol. 63, pp. 473–484, Dec. 2014, doi: 10.1016/j.ijepes.2014.06.025.

- [5] J. Zhou, R. Q. Hu and Y. Qian, "Scalable distributed communication architectures to support advanced metering infrastructure in smart grid," *IEEE Transactions on Parallel and Distributed Systems*, vol. 23, no. 9, pp. 1632-1642, Sept. 2012, doi: 10.1109/TPDS.2012.53.

- [6] J. Jiang and Y. Qian, "Distributed communication architecture for smart grid applications," *IEEE Communications Magazine*, vol. 54, no. 12, pp. 60-67, December 2016, doi: 10.1109/MCOM.2016.1600321CM.

- [7] M. Kuzlu, M. Pipattanasomporn, and S. Rahman, "Communication network requirements for major smart grid applications in HAN, NAN and WAN," *Computer Networks*, vol. 67, pp. 74–88, Jul. 2014, doi: 10.1016/j.comnet.2014.03.029.

- [8] S. Reka. S, T. Dragičević, P. Siano, and S. R. S. Prabaharan, "Future generation 5G wireless networks for smart grid: a comprehensive review," *Energies*, vol. 12, no. 11, p. 2140, Jun. 2019, doi: 10.3390/en12112140.

- [9] C. Liu and C.-J. R. Shi, "Design of the class-e power amplifier considering the temperature effect of the transistor on-resistance for sensor applications," *IEEE Trans. Circuits Syst. II*, vol. 68, no. 5, pp. 1705–1709, May 2021, doi: 10.1109/TCSII.2021.3066963.

- [10] C. Lee and C. Park, "Switching-mode CMOS power amplifier using a differentially coupled series inductor," Progress in Electromagnetics Research Letters, vol. 81, pp. 59–64, 2019, doi: 10.2528/PIERL18102506.

- [11] B. Park et al., "Highly linear mm-wave CMOS power amplifier," *IEEE Transactions on Microwave Theory and Techniques*, vol. 64, no. 12, pp. 4535–4544, Dec. 2016, doi: 10.1109/TMTT.2016.2623706.

- [12] K. Kunihiro, S. Hori, and T. Kaneko, "High-efficiency power amplifiers for mobile base stations: recent trends and future prospects for 5G," *IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences*, vol. E101.A, no. 2, pp. 374–384, 2018, doi: 10.1587/transfun.E101.A.374.

- [13] P. Reynaert, Y. Cao, M. Vigilante and P. Indirayanti, "Doherty techniques for 5G RF and mm-wave power amplifiers," 2016 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 2016, pp. 1-2, doi: 10.1109/VLSI-TSA.2016.7480475.

- [14] P. M. Asbeck, "Will Doherty continue to rule for 5G?," 2016 IEEE MTT-S International Microwave Symposium (IMS), San Francisco, CA, USA, 2016, pp. 1-4, doi: 10.1109/MWSYM.2016.7540208.

- [15] M. Li, J. Pang, Y. Li, and A. Zhu, "Ultra-wideband dual-mode doherty power amplifier using reciprocal gate bias for 5G applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 67, no. 10, pp. 4246–4259, Oct. 2019, doi: 10.1109/TMTT.2019.2932977.

- [16] P. Wright, J. Lees, J. Benedikt, P. J. Tasker and S. C. Cripps, "A methodology for realizing high efficiency class-J in a linear and broadband PA," *IEEE Transactions on Microwave Theory and Techniques*, vol. 57, no. 12, pp. 3196-3204, Dec. 2009, doi: 10.1109/TMTT.2009.2033295.

- [17] S. Rezaei, L. Belostotski, F. M. Ghannouchi and P. Aflaki, "Integrated design of a class-J power amplifier," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 61, no. 4, pp. 1639-1648, April 2013, doi: 10.1109/TMTT.2013.2247618.

- [18] Y. Dong, L. Mao and S. Xie, "Fully integrated class-J power amplifier in standard CMOS technology," *IEEE Microwave and Wireless Components Letters*, vol. 27, no. 1, pp. 64-66, Jan. 2017, doi: 10.1109/LMWC.2016.2630920.

- [19] A. Alizadeh, M. Frounchi and A. Medi, "Waveform engineering at gate node of class-J power amplifiers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 7, pp. 2409-2417, Jul. 2017, doi: 10.1109/TMTT.2017.2651814.

- [20] A. Alizadeh and A. Medi, "Investigation of a class-J mode power amplifier in presence of a second-harmonic voltage at the gate node of the transistor," *IEEE Transactions on Microwave Theory and Techniques*, vol. 65, no. 8, pp. 3024-3033, Aug. 2017, doi: 10.1109/TMTT.2017.2666145.

- [21] T. Hanna, N. Deltimple, and S. Frégonèse, "A class-J power amplifier for 5G applications in 28 nm CMOS FD-SOI technology," 2017 30th Symposium on Integrated Circuits and Systems Design (SBCCI), Fortaleza Ceará Brazil, Aug. 2017, pp. 110–113, doi: 10.1145/3109984.3110018

- [22] B. Liu, M. Mao, C. C. Boon, P. Choi, D. Khanna and E. A. Fitzgerald, "A fully integrated class-J GaN MMIC power amplifier for 5-GHz WLAN 802.11ax application," *IEEE Microwave and Wireless Components Letters*, vol. 28, no. 5, pp. 434-436, May 2018, doi: 10.1109/LMWC.2018.2811338.

- [23] W. Gao, Y. Luo, C. Shen and R. Lei, "Design of class-J power amplifier with dynamic matching network for 5G frequency band," 2020 IEEE 20th International Conference on Communication Technology (ICCT), Nanning, China, 2020, pp. 472-475, doi: 10.1109/ICCT50939.2020.9295827.

- [24] A. Alizadeh, S. Hassanzadehyamchi, A. Medi and S. Kiaei, "An X-Band class-J power amplifier with active load modulation to boost drain efficiency," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 67, no. 10, pp. 3364-3377, Oct. 2020, doi: 10.1109/TCSI.2020.2991184.

- [25] P. Zhang et al., "An X-band broadband high-efficiency power amplifier with class-J mode matching network," 2021 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Nanjing, China, 2021, pp. 1-3, doi: 10.1109/ICMMT52847.2021.9617933.

- [26] A. Nasri et al., "Broadband class-J GaN Doherty power amplifier," Electronics (Switzerland), vol. 11, no. 4, p. 552, Feb. 2022, doi: 10.3390/electronics11040552.

- [27] J. N. Burghartz and B. Rejaei, "On the design of RF spiral inductors on silicon," *IEEE Transactions on Electron Devices*, vol. 50, no. 3, pp. 718-729, March 2003, doi: 10.1109/TED.2003.810474.

- [28] M. Mhiri and K. Besbes, "Gyrator-c-based CMOS active inductors: analysis of performance optimization techniques," *IEEE Microwave Magazine*, vol. 22, no. 8, pp. 65-82, Aug. 2021, doi: 10.1109/MMM.2021.3078041.

- [29] A. S. Sayem, S. Rashid, S. Akter, O. Faruqe and M. Hossam-E-Haider, "Performance analysis and simulation of spiral and active inductor in 90nm CMOS technology," 2018 4th International Conference on Electrical Engineering and Information & Communication Technology (iCEEiCT), Dhaka, Bangladesh, 2018, pp. 571-576, doi: 10.1109/CEEICT.2018.8628046.

- [30] A.Saberkari, S. Ziabakhsh, H. Martinez, and E. Alarcón, "Active inductor-based tunable impedance matching network for RF power amplifier application," *Integration*, vol. 52, pp. 301–308, Jan. 2016, doi: 10.1016/j.vlsi.2015.07.013.

- [31] O. Faruqe and M. T. Amin, "Wide tuning range varactorless tunable active inductor-based voltage controlled oscillator for wireless applications," *Journal of Circuits, Systems and Computers*, vol. 28, no. 14, p. 1950242, Dec. 2019, doi: 10.1142/S0218126619502426.

- [32] R. C. Gurjar and D. K. Mishra, "Design and performance analysis of active inductor with low voltage and high Q factor," 2020 International Conference on Inventive Computation Technologies (ICICT), Coimbatore, India, Feb. 2020, pp. 1027–1030, doi: 10.1109/ICICT48043.2020.9112505.

- [33] Y. K. Hiew, N. M. Aripin, S. Jayavalan and N. M. Din, "Spectrum band for smart grid implementation in Malaysia," 2013 IEEE Student Conference on Research and Development, Putrajaya, Malaysia, 2013, pp. 26-30, doi: 10.1109/SCOReD.2013.7002534.

- [34] M. Roslee, A. Alhammadi, M. Y. Alias, K. Anuar and P. U. Nmenme, "Efficient handoff spectrum scheme using fuzzy decision making in cognitive radio system," 2017 3rd International Conference on Frontiers of Signal Processing (ICFSP), Paris, France, 2017, pp. 72-75, doi: 10.1109/ICFSP.2017.8097144.

- [35] Parvez and A. I. Sarwat, "A spectrum sharing based metering infrastructure for smart grid utilizing LTE and WiFi," *Advances in Science, Technology and Engineering Systems Journal*, vol. 4, no. 2, pp. 70–77, 2019, doi: 10.25046/aj040209.

- [36] K. H. Hamza and D. Nirmal, "A review of GaN HEMT broadband power amplifiers," AEU International Journal of Electronics and Communications, vol. 116, p. 153040, Mar. 2020, doi: 10.1016/j.aeue.2019.153040.

# **BIOGRAPHIES OF AUTHORS**

Nagisetty Sridhar D S received his B.E. degree in electrical and electronics engineering from SASTRA University, Thanjavur, Tamil Nadu, India, in 2009 and his master's degree in power electronics and drives from Jerusalem College of Engineering, Anna University, Chennai, Tamil Nadu, India, in 2011. He has 8 years of teaching experience in various engineering colleges and universities. Presently he is pursuing his Ph.D. degree in the Faculty of Engineering, Multimedia University-Cyberjaya campus, Malaysia. His research interests include multilevel inverters, 5G power amplifiers, and active inductors. He can be contacted at email: sridharnagisetty@gmail.com.

Chinnaiyan Senthilpari (i) (senior member, IEEE) received the M.Sc. degree in applied electronics and the M.E. degree in material science from the National Institute of Technology, Tiruchirappalli, and the Ph.D. degree from Multimedia University, in 2009. He joined Multimedia University, Malaysia, as a lecturer, in 2005. His research work focuses on the VLSI design and simulation analysis of new hardware circuits. He was invited as a committee member of various international conferences. His research interests are in the chosen area of specialization. He is currently guiding the master's and Ph.D. students while teaching at the undergraduate and postgraduate levels. He successfully researched VLSI design with 150 bachelor's students, one master's student, and four Ph.D. students. He is a member of IET, U.K. He received recognition from IET as a Chartered Engineer. He can be contacted at email: c.senthilpari@mmu.edu.my.

Mardeni Roslee (1) State (senior member, IEEE) is a professor and chairman of Centre for Wireless Technology, Faculty of Engineering, Multimedia University since 2008. His current research interests are 5G/6G telecommunication, D2D, satellite, Internet of Things and radar communication. He is the former deputy director of Research Management Centre and was President of MMU staff association, Multimedia University. At international/local level, he was a chairman of IEEE Malaysia in Comsoc/VTS. He is a registered chartered engineer with Engineering Council United Kingdom, and member with the Institution of Engineering and Technology (IET), UK. He was invited as keynote speaker for 20 international conferences and been invited by IEEE international conference at 16 different countries such as at Thailand, China, Australia, Korea, Indonesia, Singapore, Japan, French, United Kingdom, Spain, Canada, New Zealand, Romania, India and Turkey for 2009-2023. He has hold as general chair of some IEEE international conference such as WCASET22, IEEE ICEET22, DIFCON21, IEEE MICC21, IEEE ICECCE21, IEEE ISTT20 and IEEE MICC2019, His contributions to academic and the engineering professional over the years have earned him recognitions nationally and internationally, he has awarded more than 100 International/local awards including IEEE outstanding large chapter award for 2019 and 2020, 2021 IEEE Malaysia outstanding volunteer award and winner of top research scientist in Malaysia 2020 from Academy of Science Malaysia (ASM). He can be contacted at email: mardeni.roslee@mmu.edu.my.

Wong Hin Yong (b) (senior member, IEEE) received the B.Eng. (Hons.) degree from the University of Sussex, U.K., the M.Sc. (Eng) (Hons.) degree from the University of Leeds, U.K., and the Ph.D. degree in electronic and electrical engineering from the University of Glasgow, U.K. He joined Multimedia University (MMU), Cyberjaya, as a pioneer staff member, where he has been a lecturer with the Faculty of Engineering, since 1999. Since 1999, he has been a senior lecturer, an associate professor with the Research Institute Digital Enterprise, where he is currently a professor and the director. He was the dean of the Faculty of Engineering for almost eight years overseeing more than 120 staff and 15 engineering bachelor's and master's programmes. During his tenure as the dean, he is proud to witness the growth of the faculty from strength to strength. Some of the notable achievements were full accreditation was granted for all the engineering programmes under his care, development of new postgraduate engineering programmes, high number of staff with professional engineers and equivalent qualification for all programmes, the establishment of Graduate Institute of Engineering, average graduate employability of the engineering graduates of above 97%, MMU being ranked Top 200 in the world by QS working ranking exercise for the discipline of electrical and electronic engineering and many more he has witness He is also supervising/cosupervising over 30 Ph.D. and master's students where many of them have successfully graduated, completed thesis and on thesis writing up stages. He has published book chapter, review chapter, encyclopedia, and 100 international research articles in renowned ISI and Scopus indexed journals and conferences based on his research findings. He has successfully secured a total research grant of over RM 4.9 million for his research projects from various external funding sources His expertise covers wireless communication, semiconductor, nanotechnology, photonics and renewable energy. His research expertise established has resulted in invitations to provide consultancy services to many multi-national companies and wafer foundries. He was a recipient to many prestigious scholastic awards, such the U.K. Tetley and Lupton Scholarship Award, the Overseas Research Students (ORS) Awards, U.K., and the University of Glasgow Postgraduate Research Scholarship awards. He can be contacted at email: hywong@mmu.edu.my.