# Design and memory optimization of hybrid gate diffusion input numerical controlled oscillator

## Ramana Reddy Gujjula<sup>1</sup>, Chitra Perumal<sup>2</sup>, Prakash Kodali<sup>3</sup>, Bodapati Venkata Rajanna<sup>4</sup>

<sup>1</sup>Department of Electronics and Communication Engineering, Sathyabama Institute of Science and Technology, Chennai, India <sup>2</sup>Department of Electronics and Communication Engineering, Faculty of Engineering, Sathyabama Institute of Science and Technology, Chennai, India

<sup>3</sup>Department of Electronics and Communication Engineering, Faculty of Engineering, National Institute of Technology Warangal, Warangal, India

<sup>4</sup>Department of Electrical and Electronics Engineering, Faculty of Engineering, RK College of Engineering, Vijayawada, India

### **Article Info**

# Article history:

Received Jul 18, 2022 Revised Aug 7, 2022 Accepted Aug 27, 2022

### Keywords:

Digital to analog converter Direct digital synthesizers Field programmable gate array Gate diffusion input Numerically controlled oscillator

## ABSTRACT

The numerically controlled oscillator (NCO) is one of the digital oscillator signal generators. It can generate the clocked, synchronous, discrete waveform, and generally sinusoidal. Often NCOs care utilized in the combinations of digital to analog converter (DAC) at the outputs for creating direct digital synthesizer (DDS). The network on chips (NOCs) are utilized in various communication systems that are fully digital or mixed signals such as synthesis of arbitrary wave, precise control for sonar systems or phased array radar, digital down/up converters, all the digital phase locked loops (PLLs) for cellular and personal communication system (PCS) base stations and drivers for acoustic or optical transmissions and multilevel phase shift keying/frequency shift keying (PSK/FSK) modulators or demodulators (modem). The basic architecture of NCO will be enhanced and improved with less hardware for facilitating complete system level support to various sorts of modulation with minimum FPGA resources. In this paper design and memory optimization of hybrid gate diffusion input (GDI) numerically controlled oscillator based on field programmable gate array (FPGA) is implemented. compared with NCO based 8-bit microchip, memory optimization of hybrid GDI numerically controlled oscillator based on FPGA gives effective outcome in terms of delay, metal-oxidesemiconductor field-effect transistors (MOSFET's) and nodes.

This is an open access article under the <u>CC BY-SA</u> license.

### **Corresponding Author:**

Chitra Perumal

Department of Electronics and Communication Engineering, Faculty of Engineering Sathyabama Institute of Science and Technology Jeppiaar Nagar, Rajiv Gandhi Salai, Chennai-600119, Tamilnadu, India Email: chitra.jegatheesan@gmail.com

# 1. INTRODUCTION

Since its inception the communication fields have been noticed many enhancements. Some of the reasons behind it are the requirements of good design, efficiency of power and area [1]. In communication devices the most important block is numerically controlled oscillator (NCO). The NCO is one of the computerized signal generators which can generate discrete-time, synchronous (timed) and discrete esteemed waveform representational basically sinusoidal.

Usually the NCOs can be used as the part of conjunction with digital to analog converter (DAC) at the output side for makingdirect digital synthesizer (DDS). The NCO provides a certain focal point over various types of oscillators regarding security, quality of unwavering, exactness and quality. The NCO can be used as

the segment of corresponding frameworks include computerized up/down converters which are utilized inadvanced PLLs, programming radio frameworks and 3G remote, multi-level phase shift keying/frequency shift keying (PSK/FSK)demodulators or modulators (modem)and drivers for the transmission of acoustics or optic [2]–[4].

The NCO is an electronic architecture to incorporate the scope of frequencies from changing time base. Unlike a simple recurrence synthesizer based on stage bolted circle, the NCO fits to combine the extensive varieties of exact recurrence proportions [5]–[8]. In addition, the NCOs are known as DDS, is an intensive technique used as the part of radio recurrence signals era to use in utilizations assortment from radio collectors for signs generators and certain more.

The basic NCO uses time space sufficiency tests for sinusoidal waveform creation and its recurrence can be controlled through the computerized control word in solitary time clock cycle. The output recurrence of NCOs may alter right away with no procurement and lock delay times are associated with classical phase locked loop (PLL) synthesizers. The yield recurrence of NCO is observed by the info check/entire number quality. Fundamentally inside the NCO center is comprised with stage gatherer and a stage to plentifulness converter (PAC) [9]–[12].Two or more look up tables (LUTs), that can store the samples of cosine and sine waveforms are used by the larger portion of PACs and the stage to-sufficiency transformation is finished by some related rationale.

The DDS is one of the most popular and widely utilized synthesizers in digital systems include digital communication where they can be utilized for sinusoidal sequences generation. In most of the implementation the DDS will be in voltage-controlled oscillator (VCO) form or in digital world it is named as NCO. Here, "control" means changing the oscillator output frequency by a control input [13]–[17].

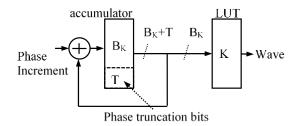

The LUT-based NCOs are used majority as they are analyzed first. The simplest NCOs including phase accumulator, certain output bits of which can drive the address inputs of read only memory (ROM) filled with sinusoidal samples is as shown in Figure 1. If the input of accumulator is changed then the frequency of output will be controlled. The frequency finer controller is allowed by the phase truncation bits. In many cases where field programmable gate arrays (FPGAs) are employed, NCO tables are actually random-access memory (RAMs) whose contents are altered in operating conditions providing great flexibility. Therefore LUT based network on chips (NOCs) are well suited in digital designs with FPGAs [18]–[21].

Figure 1. Basic table based NCO

However, the LUT based NOCs tending for consumption of more power for more memory and the memory circuits may draw power even when they are not accessed. Therefore, authors aimed to reduce/compress memory size while preserving the quality of output signal. The studies ranging from the employment of certain trigonometric identities for linear/nonlinear interpolation between the sample points stored in the ROM.

One of the most used quality measures for generated sinusoidal is spurious free dynamic range (SFDR) that can give the amplitude differences between targeted frequency component and further strongest component over the frequency spectrum. This SFDR offers an idea over generated signal spectral purity and the higher will be better. In quadrature NOCs same quality measures are utilized i.e., sine and cosine signal at output [22].

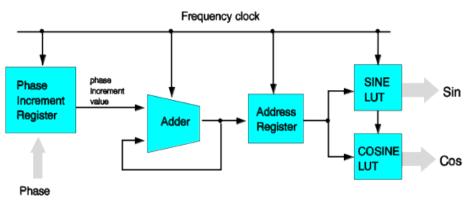

The NCO sometimes called a local oscillator which generates digital samples of two sine waves precisely offset by 90 degrees during phase creation of cosine as well as sine signals. This can use the sine/cosine LUTs and a digital phase accumulator (i.e., adder). The clock of analog to digital converter (ADC) is passing through the local oscillator. The local oscillator generates the digital samples with the sample rate which can exactly equal to the clock frequency of ADC sample i.e. fs. As the data rates from the two mixer input sources would be at the sampling rate of ADC i.e., fs and the output samples of complex mixer are at fs. The local oscillator sine and cosine input will create an In-phase and quadrature (I and Q) output which would be vital to maintain the phase information of an input signal.

The decimating low pass filter (LPF) may accept the input samples from the output of mixer at full sampling frequency (fs) of ADC. It may use the digital signal processing (DSP) for the implementation offinite impulse response (FIR) filter transfer function. This filter allows the passage of all signals from 0 Hz to a programmable bandwidth or cutoff frequency and rejects the signals which can have frequency above cutoff [23]. Digital filter is one of the most complex filters that will process I and Q signals from mixer. The conventional NCO is shown in Figure 2.

Figure 2. Conventional NCO

# 2. NUMERICALLY CONTROLLED OSCILLATOR FOR MICROCHIP 8-BIT MCU

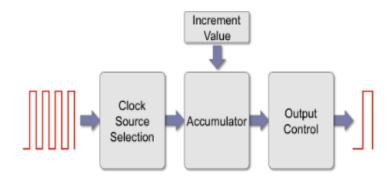

Thenumerically controlled oscillator (NCOx) module shown in Figure 3 is a timer and it utilizes an accumulator overflow for output signal generation. The overflow of accumulator can be controlled with the adjustable increment value instead of post-scaler increment or single clock pulse. This may offer an advantage on simpler time driven counter where division resolution won't change with limited postscaler/prescaler divider values [24]. The NCOx module is mostly useful for the applications which may need fine resolution and frequency accuracy at a fixed duty cycle (FDC). Features of the NCOx include:

- 16-bit increment function

- Multiple clock input sources

- FDC mode

- Interrupt capability

- Output polarity control

- Output pulse width control

- Pulse Frequency (PF) mode

Figure 3. Numerically controlled oscillator for microchip 8-bit MCU

The NCOx is operated by adding the fixed value repeatedly to the accumulator. The additions will appear at input clock rate. The accumulator is overflowed with the carry periodically that is the raw output of NCOx. This will effectively reduce the input clock by a ratio of added value to the maximum value of accumulator.

**D** 81

Further the output of NCOx is modified by toggling a flip-flop or stretching the pulse. Then modified NCOx output can be internally distributed to peripherals and optionally output to I/O pin. An interrupt is generated by the overflow of accumulator. The period of NCOx is varying in discrete steps for average frequency creation. Based in the abilities of receiving circuit (i.e., external resonant converter circuitry) this output averages the output of NCOx for reducing uncertainty [25].

The NCO module overflow is expressed as:

Accumulator Overflow Rate = Accumulator Overflow Value Input Clock Frequency × Increment Value

the NCO module may provide the output signal in any of two modes namely: i) fixed duty cycle and ii) pulse frequency modulation.

The FDC mode will toggle the output on every flow of accumulator. If the clock and adder values do not change then this results 50% duty cycle as output. The PF modulation triggers the pulse on every overflow of accumulator to the period set by 3 bits in numerically controlled oscillator (NCO) register. The accumulator is a 20-bit register and it can have maximum value of 1,048,575. The accumulators write and read access is available by the registers:

- NCOxACCL

- NCOxACCH

- NCOxACCU

The NCOx adder is a full adder that will operate independently from a system clock. This can add the increment values to accumulator over every clock pulse of NCO. This adder will take the value from accumulator and it is added to increment value and the obtained result is stored in the accumulator. The value of accumulator is roll over and the value beyond 1,048,575 is stored as initial value in the accumulator. When a zero is written to the accumulator then it is reset. Normally this can be done in Interrupt Service Routine (ISR) when it is enabled over NCOx module [25]. The increment value will be stored in two 8-bit registers made as a 16-bit increment value. The upper 8 bits might be stored in NCOxINCH register and lower 8-bits will be stored in NCOxINCL register.

- NCOxINCL

- NCOxINCH

These registers are writeable as well as readable. These increment registers would be doublebuffered for allowing to the value changes to be done and no need to disable the NCOx module. if the module is disabled then the buffer loads will be immediate. Writing the values into the NCOxINCH register is essential since the buffer would be synchronously loaded with the operations of NCOx module after the write is performed on NCOxINCL register. The available clock sources to NCOx are:

- HFINTOSC

- CLKIN pin

- LCxOUT

- FOSC

Configure the NxCKS<2:0> bits in NCOxCLK register for NCOx module clock source selection. However, the NCO output has various options which might be set in NCOCON register. The output will enable or disable ((NxOE bit) and even invert (NxPOL bit) while clearing or setting the bits in NCOCON register. In addition, the output is monitored in software by reading the NxOUT bit state in NCOCON register. The output of NCO triggers the internal interrupt if the accumulator is overflowed. This will be handled with 3 bits (NCOxIE, GIE and PEIE). This can allow the NCO for controlling the actions of software via ISR in application code and also result a signal to the I/O pin.GIE referred as Global Interrupt Enable bit, NCOxIE is referred as NCO Interrupt Enable bit. Multiple NCO modules will be there. Here "x" indicates NCO number and PEIE is Peripheral Interrupt Enable bit. The NCOxIF bit is an Interrupt Indicator Flag. In software, this is monitored for observing that interrupt is occurred or not. This is required to be cleared in ISR or in software routine which can read the bit.

#### 3. MEMORY OPTIMIZATION OF HYBRID GDI NUMERICAL CONTROLLED OSCILLATOR

One of the most important parts of digital down conversion is NCO. The NCO is most widely utilized in software radio systems as well as in radar wireless transceiver systems. Here the NCO major function is producing two path sine and cosine data samples with discrete time, variable frequency and mutually orthogonal. The main advantage of NCO is quick response and high frequency precision. The LUT and polynomial expansion are the traditional implementation methods of NCO. The LUT method data accuracy depends on the LUT size of ROM. The memory size and phase accuracy precision are the exponential relationships that will enlarge the consumption of resources and reduce the system processing speed.

As known that NCO is one of the most utilized digital oscillators that generate signals like clocked, discrete and synchronous waveforms. The NOCs are more often utilized in combinations with the DAC at the outputs for creating DDS. The NCO is utilized in various communication systems that are fully digital or mixed signal such as synthesis of arbitrary waveform, phased array radar and precise control.

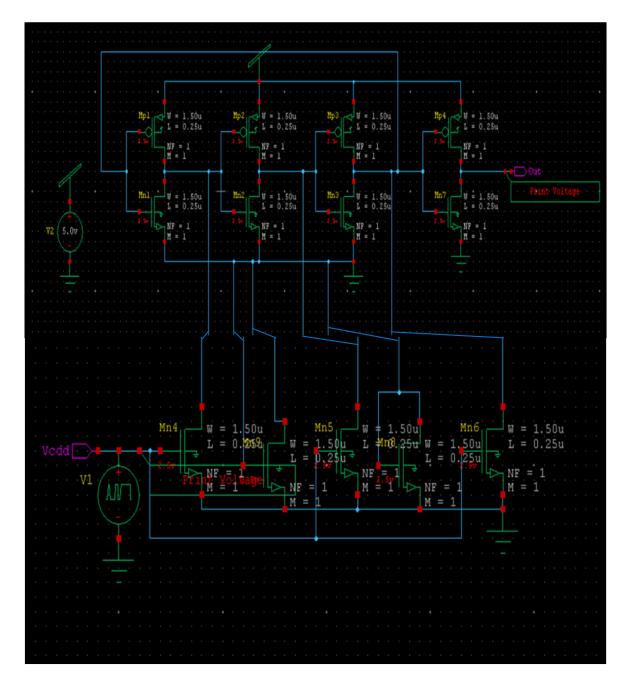

Figure 4 shows the schematic of memory optimization of hybrid GDI NCO. In this 16 metal-oxidesemiconductor field-effect transistors (MOSFET's) are utilized to design. 2 MOSFET's geometries are utilized. Basically, Total nodes are classified into two types of boundary nodes and independent nodes.1.70 seconds is taken to execute the entire seconds. 0.14 seconds is taken for parsing and 0.03 seconds is taken for setup the design. 12 total nodes are utilized, 5 boundary nodes and 7 independent nodes are utilized. Compared with NCO based 8-bit microchip design, memory optimization of hybrid GDI based NCO gives effective outcome in terms of delay, MOSFET's and nodes. The output waveform is shown in Figure 5.

Figure 4. Schematic design

| nner T-Spice 16 | .01 C | :\Users\DEL | L\AppData | \Local\Tem | p\PROPO | SED.sp | 15:43:31 0 | ₄/19/2 |

|-----------------|-------|-------------|-----------|------------|---------|--------|------------|--------|

| 000             |       |             |           |            |         |        |            |        |

| 500 -           |       |             |           |            |         |        |            |        |

| 000             |       |             |           |            |         |        |            |        |

| 500             |       |             |           |            |         |        |            |        |

| 000 -           |       |             |           |            |         |        |            |        |

| 500             |       |             |           |            |         |        |            |        |

| 000             |       |             |           |            |         |        |            |        |

| 500 -           |       |             |           |            |         |        |            |        |

| 000             |       |             |           |            |         |        |            |        |

| 500             |       |             |           |            |         |        |            |        |

| 000 - 🗉 💷 📕     |       |             |           |            |         |        |            |        |

| - Out V         |       |             |           |            |         |        |            |        |

| 300             |       |             |           |            |         |        |            |        |

|                 |       |             |           |            |         |        |            |        |

| 250             |       |             |           |            |         |        |            |        |

| 200             |       |             |           |            |         |        |            |        |

|                 |       |             |           |            |         |        |            |        |

| 150             |       |             |           |            |         |        |            |        |

| 100             |       |             |           |            |         |        |            |        |

| 100             |       |             |           |            |         |        |            |        |

| 050             |       |             |           |            |         |        |            |        |

|                 |       |             |           |            |         |        |            |        |

Figure 5. Output waveform

# 4. RESULTS AND DISCUSSION

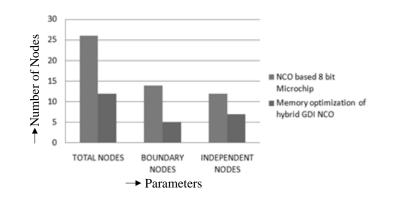

Table 1 shows the comparison table. In this 16 MOSFET's are utilized to design. 12 total nodes are utilized, 5 boundary nodes and 7 independent nodes are utilized. 2 MOSFET's geometries are utilized. 1.70 seconds is taken to execute the entire seconds. 0.14 seconds is taken for parsing and 0.03 seconds is taken for setup the design. Figure 6 shows the comparison of nodes for memory optimization of hybrid GDI NCO and NCO based 8-bitmicrochip. Compared with NCO based 8-bitmicrochip, Memory optimization of hybrid GDI NCO uses less number of nodes.

Table 1. Comparison table

| S. No | Parameters          | NCO based 8-bitmicrochip | Memory optimization of hybrid GDI NCO |

|-------|---------------------|--------------------------|---------------------------------------|

| 1     | MOSFET's            | 32                       | 16                                    |

| 2     | MOSFET's geometries | 5                        | 2                                     |

| 2     | Voltage sources     | 8                        | 4                                     |

| 3     | Total nodes         | 26                       | 12                                    |

| 4     | Boundary nodes      | 14                       | 5                                     |

| 5     | Independent nodes   | 12                       | 7                                     |

| 6     | Total delay         | 2.51 Seconds             | 1.70 Seconds                          |

| 7     | Parsing delay       | 0.43Seconds              | 0.14 Seconds                          |

| 8     | Setup delay         | 0.06 Seconds             | 0.03 Seconds                          |

Design and memory optimization of hybrid gate diffusion input numerical ... (Ramana Reddy Gujjula)

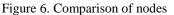

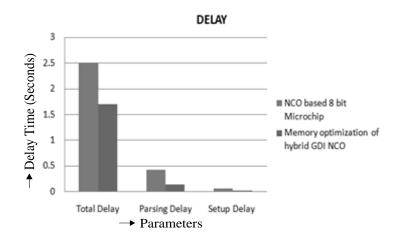

Figure 7 shows the comparison of delay for memory optimization of hybrid GDI NCO and NCO based 8-bitmicrochip. Compared with NCO based 8-bitmicrochip, memory optimization of hybrid GDI NCO produces less delay. Figure 8 shows the comparison of MOSFET's for memory optimization of hybrid GDI NCO and NCO based 8-bitmicrochip. Compared with NCO based 8-bitmicrochip, memory optimization of hybrid GDI NCO uses less MOSFET's.

Figure 7. Comparison of delay

Figure 8. Comparison of MOSFET's

## 5. CONCLUSION

Hence in this paper design and memory optimization of hybrid GDI numerically controlled oscillator based on FPGA was implemented. compared with NCO based 8-bit microchip, memory optimization of hybrid GDI numerically controlled oscillator based on FPGA gives effective outcome in terms of delay, MOSFET's and Nodes. In this 16 MOSFET's are utilized to design. 2 MOSFET's geometries are utilized. Basically, Total nodes are classified into two types of boundary nodes and independent nodes. 1.70 seconds is taken to execute the entire seconds. 0.14 seconds is taken for parsing and 0.03 seconds is taken for setup the design. 12 total nodes are utilized, 5 boundary nodes and 7 independent nodes are utilized. Compared with NCO based 8-bit microchip design, memory optimization of hybrid GDI based NCO gives effective outcome in terms of delay, MOSFET's and nodes.

#### REFERENCES

S. R. Rupanagudi et al., "Design of a low power digital down converter for 802.16m - 4G WiMAX on FPGA," in 2014 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Sep. 2014, pp. 2303–2308. doi: 10.1109/ICACCI.2014.6968583.

- [2] S. R. Huddar, S. R. Rupanagudi, M. Kalpana, and S. Mohan, "Novel high speed vedic mathematics multiplier using compressors," in 2013 International Multi-Conference on Automation, Computing, Communication, Control and Compressed Sensing (iMac4s), Mar. 2013, pp. 465–469. doi: 10.1109/iMac4s.2013.6526456.

- [3] S. R. Rupanagudi et al., "A low area and low power SOC design for the baseband demodulator of an indoor local positioning system," in 2015 International Conference on Computing and Network Communications (CoCoNet), Dec. 2015, pp. 689–695. doi: 10.1109/CoCoNet.2015.7411265.

- [4] S. R. Huddar, S. R. Rupanagudi, R. Ravi, S. Yadav, and S. Jain, "Novel architecture for inverse mix columns for AES using ancient Vedic mathematics on FPGA," in 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), Aug. 2013, pp. 1924–1929. doi: 10.1109/ICACCI.2013.6637476.

- [5] R. P. Mistry and S. Oza, "Survey of optimization of NCO for digital communication systems," *Journal of Information, Knowledge and Research in Electronics and communication engineering*, vol. 2, no. 2, pp. 725–728, 2013.

- [6] G. D. Ghiwala, "Realization of FPGA based numerically Controlled Oscillator," *IOSR journal of VLSI and Signal Processing*, vol. 1, no. 5, pp. 7–11, 2013, doi: 10.9790/4200-0150711.

- [7] S. Golestan, F. D. Freijedo, and J. M. Guerrero, "A systematic approach to design higher-order phase locked loops," *IEEE Transactions on Power Electronics*, vol. 30, no. 6, pp. 2885–2890, Jun. 2015, doi: 10.1109/TPEL.2014.2351262.

- [8] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: performance analysis and design guidelines," *IEEE Transactions on Power Electronics*, vol. 29, no. 6, pp. 2750–2763, Jun. 2014, doi: 10.1109/TPEL.2013.2273461.

- [9] F. D. Freijedo, A. G. Yepes, Ó. Lopez, P. Fernandez-Comesana, and J. Doval-Gandoy, "An optimized implementation of phase locked loops for grid applications," *IEEE Transactions on Instrumentation and Measurement*, vol. 60, no. 9, pp. 3110–3119, Sep. 2011, doi: 10.1109/TIM.2011.2122550.

- [10] F. Gonzalez-Espin, G. Garcera, I. Patrao, and E. Figueres, "An adaptive control system for threephase photovoltaic inverters working in a polluted and variable frequency electric grid," *IEEE Transactions on Power Electronics*, vol. 27, no. 10, pp. 4248– 4261, Oct. 2012, doi: 10.1109/TPEL.2012.2191623.

- [11] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Transactions on Power Electronics*, vol. 29, no. 12, pp. 6264–6270, Dec. 2014, doi: 10.1109/TPEL.2014.2329917.

- [12] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for single-phase grid-connected power conditioning systems," *IEEE Transactions on Power Electronics*, vol. 27, no. 8, pp. 3639–3650, Aug. 2012, doi: 10.1109/TPEL.2012.2183894.

- [13] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," in 2010 IEEE Energy Conversion Congress and Exposition, Sep. 2010, pp. 420–427. doi: 10.1109/ECCE.2010.5617996.

[14] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," IEEE Transactions

- [14] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Transactions on Power Delivery*, vol. 20, no. 1, pp. 300–308, Jan. 2005, doi: 10.1109/TPWRD.2004.837823.

- [15] J. E. Volder, "The CORDIC trigonometric computing technique," *IRE Transactions on Electronic Computers*, vol. EC-8, no. 3, pp. 330–334, Sep. 1959, doi: 10.1109/TEC.1959.5222693.

- [16] R. Andraka, "A survey of CORDIC algorithms for FPGA based computers," in Proceedings of the 1998 ACM/SIGDA sixth international symposium on Field programmable gate arrays - FPGA '98, 1998, pp. 191–200. doi: 10.1145/275107.275139.

- [17] K. S. T. & J. J. C. Priyanka P. Chopda, "Sine wave generation using numerically controlled oscillator module," BEST: International Journal of Management, Information Technology and Engineering (BEST: IJMITE), vol. 3, no. 7, pp. 35–40, 2015.

- [18] A. Haber, S. A. Nugroho, P. Torres, and A. F. Taha, "Control node selection algorithm for nonlinear dynamic networks," *IEEE Control Systems Letters*, vol. 5, no. 4, pp. 1195–1200, Oct. 2021, doi: 10.1109/LCSYS.2020.3019591.

- [19] J. Harzer, J. De Schutter, and M. Diehl, "Efficient numerical optimal control for highly oscillatory systems," *IEEE Control Systems Letters*, vol. 6, pp. 2719–2724, 2022, doi: 10.1109/LCSYS.2022.3175412.

- [20] M. Lu, "Virtual oscillator grid-forming inverters: state of the art, modeling, and stability," *IEEE Transactions on Power Electronics*, vol. 37, no. 10, pp. 11579–11591, Oct. 2022, doi: 10.1109/TPEL.2022.3163377.

- [21] J. Wu and X. Li, "Global stochastic synchronization of Kuramoto-oscillator networks with distributed control," *IEEE Transactions on Cybernetics*, vol. 51, no. 12, pp. 5825–5835, Dec. 2021, doi: 10.1109/TCYB.2019.2959854.

- [22] J. Wu and X. Li, "Finite-time and fixed-time synchronization of Kuramoto-oscillator network with multiplex control," *IEEE Transactions on Control of Network Systems*, vol. 6, no. 2, pp. 863–873, Jun. 2019, doi: 10.1109/TCNS.2018.2880299.

- [23] J. Zhao and T. Iwasaki, "Orbital stability analysis for perturbed nonlinear systems and natural entrainment via adaptive Andronov– Hopf oscillator," *IEEE Transactions on Automatic Control*, vol. 65, no. 1, pp. 87–101, 2020, doi: 10.1109/TAC.2019.2906429.

- [24] D. Raisz, T. T. Thai, and A. Monti, "Power control of virtual oscillator controlled inverters in grid-connected mode," *IEEE Transactions on Power Electronics*, vol. 34, no. 6, pp. 5916–5926, Jun. 2019, doi: 10.1109/TPEL.2018.2868996.

- [25] M. Lu, S. Dhople, and B. Johnson, "Benchmarking nonlinear oscillators for grid-forming inverter control," *IEEE Transactions on Power Electronics*, vol. 37, no. 9, pp. 10250–10266, Sep. 2022, doi: 10.1109/TPEL.2022.3162530.

## **BIOGRAPHIES OF AUTHORS**

**Ramana Reddy Gujjula B S S** is Research Scholar, Department of Electronics and Communication Engineering at Sathyabama Institute of Science and Technology (Deemed to be University) in Chennai, Tamilnadu State. He is working as an associate professor in the Nalanda Group of Institutions since 2007. He received many awards and did thousands of online courses including FDP in prestigious institutions and colleges. He received his post-graduation degree in the specialization of very large-scale integrated circuits concepts at Nalanda Engineering College. He has more than 14 years of teaching experience and taught a variety of updated courses for Post Graduate and Under Graduation levels. He published more than 10 papers in reputed journals and conferences related to current trends and socially relevance. He can be contacted at email: gujjula.ramanareddy@gmail.com.

Design and memory optimization of hybrid gate diffusion input numerical ... (Ramana Reddy Gujjula)

**Dr. Chitra Perumal D S S C** is Professor, Department of Electronics and Communication Engineering at Sathyabama Institute of Science and Technology (Deemed to be University) in Chennai, Tamilnadu State. She received her doctorate in the specialization of very large-scale integrated circuits concepts at Sathyabama University in September 2014. She has more than 17 years of teaching experience and taught a variety of updated courses for Post Graduate and Under Graduation levels. She published more than 25 papers in reputed journals and conferences related to current trends and social relevance. She can be contacted at email: chitra.jegatheesan@gmail.com.

**Dr. Prakash Kodali (D) (S) (S) (S) (S) (S) (S) (S) (C) (F) (C) (C**

**Dr. Bodapati Venkata Rajanna b s s** received B.Tech degree in Electrical and Electronics Engineering from Chirala Engineering College, JNTU, Kakinada, India, in 2010, M.Tech degree in Power Electronics and Drives from KoneruLakshmaiah Education Foundation, Guntur, India, in 2015 and Ph.D. in Electrical and Electronics Engineering at KoneruLakshmaiah Education Foundation, Guntur, India, in 2015 and Ph.D. in Electrical and Electronics Engineering at KoneruLakshmaiah Education Foundation, Guntur, India, in 2021. His Current Research includes, Dynamic Modeling of Batteries for Renewable Energy Storage, Electric vehicles and Portable Electronics Applications, Renewable Energy Sources Integration with Battery Energy Storage Systems (BESS), Smart Metering and Smart Grids, Micro-Grids, AMR (Automatic Meter Reading) devices, GSM/GPRS and PLC (Power Line Carrier) Communication and Various modulation techniques such as QPSK, BPSK, ASK, FSK, OOK and GMSK. Currently, he is working as an Associate Professor at R K College of Engineering, Vijayawada. He can be contacted at email: bv.rajanna@gmail.com.