# Design and software characterization of finFET based full adders

# Raju Hajare<sup>1</sup>, C.Lakshminarayana<sup>2</sup>

<sup>1</sup>Tele Communication Department, BMS Technology Institute, Bengaluru, India <sup>2</sup>Department of Electrical and Electronics Engineering, BMS College of Engineering, Bangalore, India

#### **Article Info**

#### Article history:

Received Des 8, 2018 Revised Jan 26, 2019 Accepted Feb 5, 2019

#### Keywords:

Adder CMOS Delay Finfet MOSFET Pass transistor logic Power

# **ABSTRACT**

Adder is the most important arithmetic block that are used in all processors. Most of the logical circuits till today were designed using Metal Oxide Semiconductor Field Effect Transistors (MOSFET's). In order to reduce chip area, leakage power and to increase switching speed, MOSFET's were continuously scaled down. Further scaling below 45nm, MOSFET's suffers from Short Channel Effects (SCE's) which leads to degraded performance of the Here the Performance of 28T and 16T MOSFET based 1-bit full adder cell is characterized and compared with FinFET based 28T and 16T 1-bit full adders at various technology nodes using HSPICE software. Results show that FinFET based full adder design gives better performance in terms of speed, power and reliability compared to MOSFET based full adder designs. Hence FinFET are promising candidates and better replacement for MOSFET.

Copyright © 2019 Institute of Advanced Engineering and Science.

All rights reserved.

51

# Corresponding Author:

Raju Hajare,

Department of Telecommunication Engineering,

BMS Institute of Technology, Bangalore 560064, India.

E-mail: rajuhajare@bmsit.in

# 1. INTRODUCTION

Today there is a huge demand for portable applications such as laptops, iPhones etc. with limited amount of power availability, requiring minimum area and high switching speed circuitry [1]. Therefore, circuits which provide low power consumption and high switching speed becomes the major candidates for design of microprocessor and other subsystems [2]. Addition is a basic arithmetic operation and is used in most of the VLSI subsystems like application specific DSP architectures and microprocessors [3]. Therefore, 1-bit Full Adder cell is the most important and basic block of arithmetic logic unit in digital systems.

In low power VLSI systems, Metal Oxide Semiconductor field effect Transistors (MOSFET's) are the basic transistors used in most of the digital circuits. Continuous scaling of MOSFET's has resulted in better performance of the device parameters such size, delay and power. Further scaling of MOSFET's below 45nm node technology leads to short channel effects (SCE's) which modifies the device characteristics. The major SCE's includes;

- a. Drain Induced Barrier Lowering.

- b. Velocity saturation.

- c. Hot electrons effect.

- d. Channel length modulation.

- e. Oxide breakdown.

Journal homepage: http://iaescore.com/journals/index.php/IJRES/index

To avoid these effects as well as to improve the switching speed ad to reduce the power requirements, MOSFET's were replaced by FINFET's in design circuitry [4, 5].FINFET's are multiple gate devices. These multiple gates provide better control over the channel and hence reduce the short channel effects [6]. FINFET based adder in general shows an average of 94% drop in delay, 97% decrease in power dissipation over the conventional MOSFET's [7], [8].

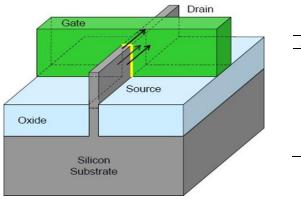

#### 2. FINFET TECHNOLOGY

FINFET known as Fin Field Effect Transistors non-planar or 3D transistor used to design modern processor. The main characteristics of FINFET is that it has a conducting channel wrapped by a thin silicon "fin" and hence the name FINFET. The thickness of the fin determines the effective channel length of the device. This wrap around gate structure provides better electrical control over the channel and this helps in reducing the leakage current and overcoming other short channel effects. This fin allows multiple gates to operate on single transistor. The multiple gates of FINFET extends Moore's Law which allows the semiconductor manufacturers to create microprocessor subsystem and memory modules that provides faster performances, less energy consumption and reduction in space complexity. 1 FinFET Structure as shown in Figure 1.

Figure 1 shows a FinFET structure. It has four terminals and it consists of source, drain and channel wrapped by multiple gates. Here we consider two gates FinFET structure namely front gate and back gate. FinFET can substitute in place of MOSFET by merely shorting the front and back gates together during device fabrication and allow FinFET work as single gate device. Table 1 shows truth table full adder.

Table 1. Full Adder Truth Table Cin Sum Cout 0 0 0 0 0 0 0 1 0 1 0 0 0 0 1 1 0 0 0 0 0 1 0 1

Figure 1. 1 FinFET structure

#### 3. 1-BIT FULL ADDER CELL

The operation of 1-bit full adder cell includes three inputs A, B, Cin using which outputs sum and carry are calculated.

Sum= $A \oplus B \oplus Cin$ Cout= $A.B+Cin. (A \oplus B)$

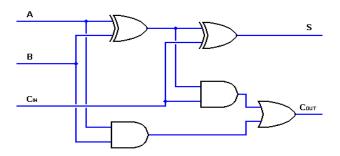

In this paper 1-bit full adder has been implemented using both CMOS and FINFET technology. Basic adder circuit as shown in Figure 2. The full adder circuitry has been designed using different logic styles:

- a. Conventional CMOS logic style.

- b. Complementary pass transistor logic and transmission gates logic.

Figure 2. Basic adder circuit

#### 4. MOSFET BASED FULL ADDER

The device parameters considered are based on predictive Technology Model (PTM) for developing a spice model and then simulating using HSPICE tool. The parameters are considered with respect to PTM as shown in the Table 2. Figure 3 shows HSPICE user interface and integration, the netlist written for a particular circuit model is characterized via the Hspice user interface and the software is powerfully integrated to find the errors and produce the output results in accurate manner.

Table 2. Design ConsiderationsParameter90nm<br/>MOSFET45nm<br/>MOSFETGate Length (Lg)90nm45nmSupply Voltage1.5V1.2V

Figure 3. Hspice user interface and integration

### 4.1. 28T Conventional CMOS Full Adder

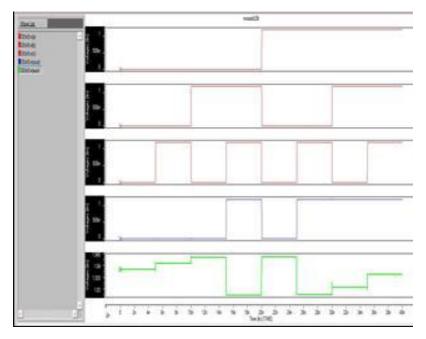

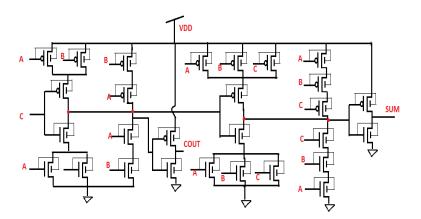

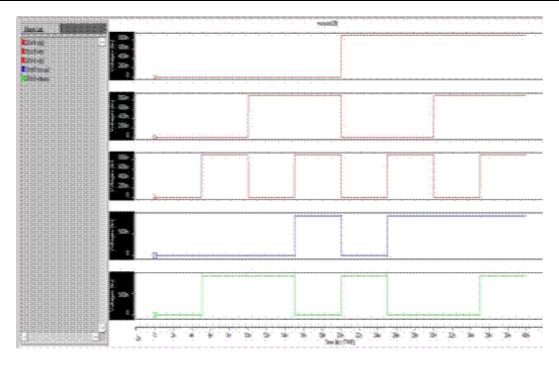

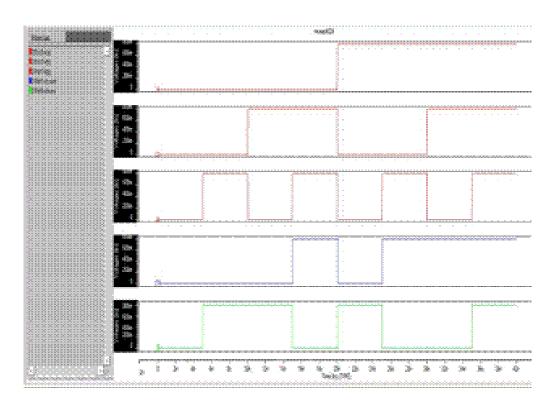

This CMOS full adder consists of both PMOS and NMOS in the form of pull-up and pull-down network. Figure 4 shows the schematic diagram of 28T conventional CMOS full adder cell. The output waveform of 28T full adder cell is as shown in Figure 5. Figure 6 shows output waveform at 45nm.

Figure 4. 28T conventional CMOS full adder

Figure 5. Output waveform at 90nm

Figure 6. Output waveform at 45nm

| Table 3. Results of 28T Full Adder Cell |                  |                  |                 |                |  |  |

|-----------------------------------------|------------------|------------------|-----------------|----------------|--|--|

| Node                                    | Average power(W) | Maximum power(W) | Sum<br>delay(s) | Carry delay(s) |  |  |

| 250nm                                   | 23.6828μ         | 1.7951m          | 211.7751p       | 136.2695p      |  |  |

| 180nm                                   | 6.5605µ          | 557.1307μ        | 176.1207p       | 112.5616p      |  |  |

| 90nm                                    | 1.1997µ          | 158.9428μ        | 66.3052p        | 45.6138p       |  |  |

| 45nm                                    | 27.3311m         | 27.4380m         | Failed          | Failed         |  |  |

From the result Table 3 it is clear that performance of MOSFET based full adder in terms of the power and delay values are obtained and it can be concluded that there is an increase in the power and delay values of MOSFET based Full Adder at 45nm node and below due to short channel effect faced by MOSFET devices.

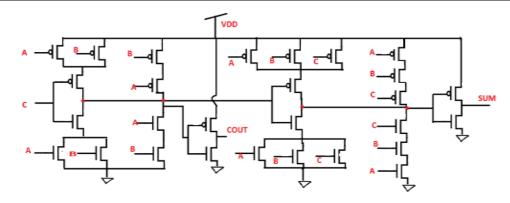

#### 4.2. 16T MOSFET Full Adder

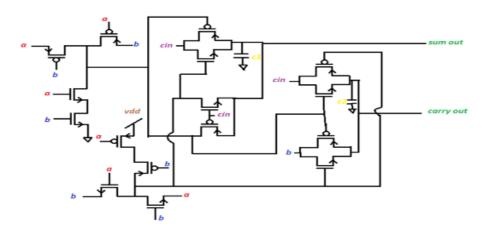

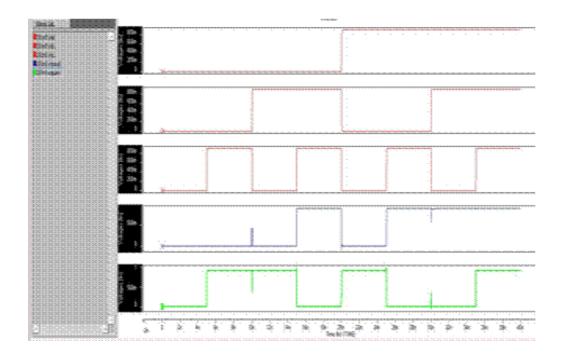

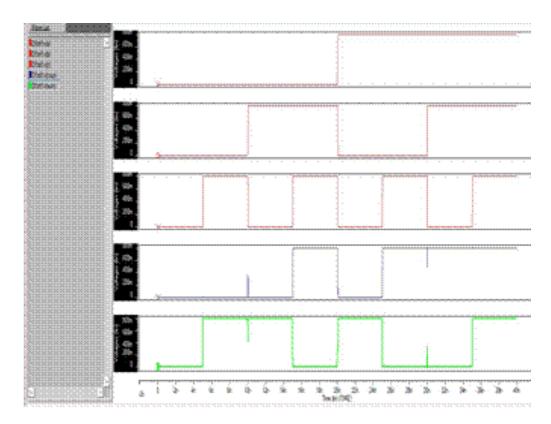

In order to reduce the number of transistors and to obtain optimum results, 16T full adder is designed and simulated using complementary pass transistors and transmission gates. The simulation is done in HSPICE tool. The schematic diagram in Figure 7 shows the design of 16T MOSFET full adder cell. Figure 8 shows output waveform at 90nm. Figure 9 shows output waveform at 45nm.

Table 4 results which contains the power and delay values for MOSFET based full adder. It is observed that there is an increase in the power and delay values of MOSFET based Full Adder at lower nodes due to short channel effect faced by MOSFET devices.

Figure 7. 16T MOSFET full adder cell

Figure 8. Output waveform at 90nm

Figure 9. Output waveform at 45nm

Table 4. Results of 16T Full Adder Cell

| Node Average Maximum Source Power(W) power(W) | Sum delay(s | )Carry delay(s) |

|-----------------------------------------------|-------------|-----------------|

| 250nm 17.0502μ 1.9958m                        | 23.6453p    | 3.6746p         |

| 180nm 3.6266µ 548.9434µ                       | 21.5174p    | 3.2325p         |

| 90nm 2.1733μ 195.1429μ                        | 15.0140p    | 2.6017p         |

| 45nm 1.8895μ 90.9523μ                         | 3.5366p     | 1.2495p         |

# 5. FinFETBASED FULL ADDER

To overcome the scaling issue faced by MOSFET, full adder cell is designed using FinFET. FinFET allows further scaling up to 14nm. Table 5 shows design considerations.

Table 5. Design Considerations

| Domomoton         | 22nm   | 14nm   |

|-------------------|--------|--------|

| Parameter         | FinFET | FinFET |

| Gate length (Lg)  | 22nm   | 14nm   |

| Supply voltage    | 0.9V   | 0.8V   |

| Fin height (hfin) | 23nm   | 30nm   |

| Fin width (tfin)  | 10nm   | 10nm   |

# 5.2. 28T FinFET Full Adder

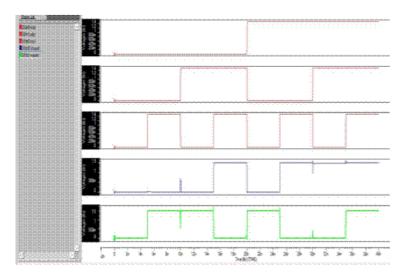

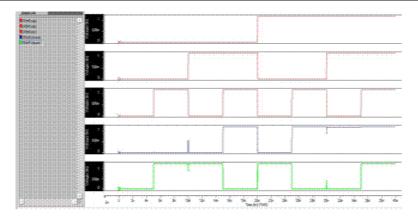

This full adder cell consists of both nFET and pFET to replace the complementary CMOS logic. The Figure 10 gives the schematic diagram of 28T FinFET full adder cell. The output waveforms of 28T full adder cell is as shown in Figure 11. From the simulated results in Figure 12 and Table 6 which contains the power and delay values for 28T FinFET based Full Adder it can concluded thatFinFET is a better replacement for MOSFET devices.

Figure 10. 28T FinFET full adder cell

Figure 11. Output waveform at 22nm

Figure 12. Output waveform at 14nm

Table 6. Results of 28T FinFETFull Adder Cell

| Node | Average power(W) | Maximum power(W) | Sum delay(s) | Carry delay(s) |

|------|------------------|------------------|--------------|----------------|

| 22nm | 62.147n          | 26.768μ          | 25.489p      | 15.966р        |

| 14nm | 32.242n          | 25.230μ          | 13.944p      | 9.7921p        |

# 5.3. 16T FinFET Full Adder

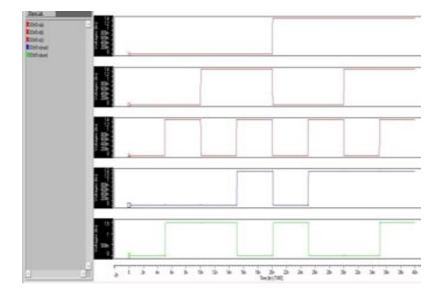

Figure 13 shows output waveform at 22nm. Figure 14 shows output waveform at 14nm. Table 7 shows results of 16T FinFET full adder cell.

Figure 13. Output waveform at 22nm

Figure 14. Output waveform at 14nm

ISSN: 2089-4864

| 1a                                     | Table 7. Results of 161 FinFE1Full Adder Cell |                          |         |        |  |  |  |

|----------------------------------------|-----------------------------------------------|--------------------------|---------|--------|--|--|--|

| Node Average Maximum power(W) power(W) |                                               | Sum delay(s) Carry delay |         |        |  |  |  |

| 22nm                                   | 35.012n                                       | 20.056μ                  | 10.503p | 2.089p |  |  |  |

| 14nm                                   | 19.721n                                       | 10.426μ                  | 8.942p  | 2.069p |  |  |  |

#### 6. RESULTS AND DISCUSSIONS

The spice models of MOSFET based full adders are created for 28T and 16T at 90nm and 45nm and are simulated using HSPICE. The simulation waveforms are viewed using Avanwaves. The comparison of the results between 28T and 16T MOSFET based full adder cell is as shown in Tables 8 and Table 9.

Table 8. Comparision of MOSFET Based Full Adder at 90nm

| No.of transistors | Average power(W) | Maximum Power | Sum delay | Carry delay(s) |

|-------------------|------------------|---------------|-----------|----------------|

| 28T               | 1.199µ           | 158.942μ      | 63.382p   | 42.161p        |

| 16T               | 1.185μ           | 93.037μ       | 13.846p   | 2.439p         |

Table 9. Comparision of MOSFET Based Full Adder at 45nm

| No.of transistors | Average power | Maximum Power | Sum delay(s) | Carry delay(s) |

|-------------------|---------------|---------------|--------------|----------------|

| 28T               | 29.321m       | 29.939m       | Failed       | 30.127p        |

| 16T               | 1.816μ        | $108.223 \mu$ | 3.536p       | 1.428p         |

From the above comparisions made we can analyse that;

- a. As number of transistors decreases, the power dissipation has decreased.

- b. Scaling of MOSFET from 90nm to 45nm has lead to increase in power dissipation. Hence further scaling down of MOSFET leads to degraded output and increase in leakage power.

The spice models based on PTM files are referred from BSIM-IMG for characterization of device and FinFET based full adders are built for 28T and 16T at 22nm and 14nm and are simulated using HSPICE. The comparison of the results between 28T and 16T FinFET based full adder cell at 22nm and 14nm nodes. is as shown in Table 10. From the above comparision of FinFET based full adder cell, we can analyse that FinFET has overcome the scaling issues of MOSFET as illustrated above at 22nm and 14nm.

Table 10. Comparision of FinFET Based Full Adder at 22nm

| No.of transistors | Average power(W) | Maximum Power(W) | Sum delay(s) | Carry delay(s) |

|-------------------|------------------|------------------|--------------|----------------|

| 28T               | 62.147n          | 26.768μ          | 25.489p      | 15.966р        |

| 16T               | 35.012n          | 20.056μ          | 10.503p      | 2.089p         |

# 7. CONCLUSION

The MOSFET and FinFET based full adder cell for 28T and 16T at different nodes are characterized using software mainly in terms of Power dissipation and delay. The obtained results for the FinFET full adder spice models used here shows a promising solution for MOSFETs scaling issues. The power dissipation in 28T FinFET based adder at 14nm is reduced to 32nW from 62nW at 22nm adder, similarly delay get reduced from 25Ps to 13.9ps when node size is reduced from 22nm to 14nm node. Likewise the results for the power and delays values for sum and carry operation are for 16T FinFET based full adders. And from the result Table 10 and 11 it can be concluded that FinFET based full adder cell is reliable at lower technology nodes and the tolerant capacity is better at the nanometer regime. The power dissipation of the FinFET based device has decreased significantly at lower technology nodes. The speeds of the adder circuits is increased terms of the sum and carry delay operation. Thus FinFET based circuits are promising candidates for the future Digital systems.

Table 11. Comparision of FinFET Based Full Adder at 14nm

| No.of transistors | Average power(W) | Maximum Power(W) | Sum delay(s) | Carry delay(s) |

|-------------------|------------------|------------------|--------------|----------------|

| 28T               | 32.242n          | 25.230μ          | 13.944p      | 9.7921p        |

| 16T               | 19.721n          | 10.426μ          | 8.942p       | 2.069p         |

# ACKNOWLEDGEMENTS

Authors thank the BMSIT and MGMT for infrastructure facility.

#### REFERENCES

[1] RuchiDantre, SudhaYadav, "esign and analysis of FinFET based high performance 1-bit half adder-half subtractor cell". Proceedings of 27<sup>th</sup> *IRF International Conference* 14<sup>th</sup> June 2015, Chennai, India, ISBN:- 978-93-85465-35-2.

- [2] Yingtao Jiang, Abdul Karim Al-Sheraidah, Yuke Wang, Edwin sha and jin-Giun Chung, "A Novel Multiplexer based Low Power Full Adder", *IEEE transaction circuits and systems*, vol 51, No.7, July 2004.

- [3] LikhithaDhulipalla, Lourts Deepak .A,"Design and implementation of 4-bit ALU using FinFETs for nano scale technology" 978-1-4673-0074-2/11/\$26.00 @2011*IEEE*

- [4] Debajit Bhattacharya and Niraj. K.Jha, "FinFETs: From Devices to Architectures". Hindawi publishing corporation, advances in Electronics Vol 2014, article ID 365689

- [5] AnindyaGhosh, DebapriyoGhosh, 'Optimization of static power, leakage power and delay of full adder circuit using dual threshold mosfet based design and Tspice simulation, 2009 *IEEE* DOI 10.1109/ARTCom. 2009.28

- [6] RajuHajare," Performance enhancement of FINFET and CNTFET at different node technologies" in Microsystem Technologies Micro- and Nano Systems Information Storage and Processing Systems, Springer, ISSN 0946-7076, MicrosystTechnol, DOI 10.1007/s00542-015-2468-9,volume 21, number 4,April 2015.

- [7] RajuHajare, "Design and Evaluation of FinFET based digital circuits for high speed ICs" International Conference on Emerging Research in Electronics, Computer Science and Technology 2015.978-1-4673-9563-2/15/2015

- [8] RajuHajare, "Performance Evaluation of FinFET and Nanowire at Different technology nodes" International Conference on Emerging Research in Electronics, Computer Science and Technology–2015,978-1-4673-9563-2/15/2015

#### **BIOGRAPHIESAUTHORS**

Raju Hajare received B.E degree in Electronics and Communication Engineering from Mysore University, India. He did his M.Tech in the field of Power Electronics from Visvesvaraya Technological University, India. He is currently working as Associate Professor in Tele Communication Department of BMS Institute of Technology, Bangalore. His areas of interest are Semiconductor Devices, Nanoelectronics and NEMS. He has Published research papers in Scopus indexed international Journals and presented papers at different international Conferences.

Dr.C. Lakshminarayana received his Ph.D. from Anna University, India. He is currently working as a Professor in Department of Electrical and Electronics Engineering, BMS College of Engineering, Bangalore. His areas of interest are Power Systems, Power Electronics Nanoelectronics. He has presented papers at different international Conferences and published papers in reputed Journals.