ISSN: 2089-4864

# Design and Implementation of Recursive Least Square Adaptive Filter Using Block DCD approach

### Sachin S. Khanande\*, S.J. Honade\*\*

\* M. E. Electronics & Telecommunication, Department of Electronics & Telecommunication Engineering

\*\* Faculty of Electronics & Telecommunication, Department of Electronics & Telecommunication Engineering

G.H. Raisoni College of Engineering, Amravati, India

# Article Info ABSTRACT Article history: Due to the ex

Received May 12, 2015 Revised Oct 9, 2015 Accepted Oct 22, 2015

# Keyword:

FPGA kit ModelSim VHDL Xilink ISE Due to the explosive growth of multimedia application and tremendous demands in Very Large Scale Integrated (VLSI), there is a need of high speed and low power digital filters for digital signal processing applications. In Digital Signal Processing (DSP) systems, Finite Impulse Response (FIR) filters are one of the most common components which is used, by convolving the input data samples with the desired unit sample response of the filter. The proposed work deals with the design and implementation of RLS adaptive filter using block DCD approach. The evaluation of speed, area and power for proposed work will be done. Also, the comparison of the proposed design with the existing will be carried out for various input combinations.

Copyright © 2015 Institute of Advanced Engineering and Science.

All rights reserved.

# Corresponding Author:

Sachin S. Khanande,

Student of M. E. Electronics & Telecommunication,

Department of Electronics & Telecommunication Engineering,

G.H. Raisoni College of Engineering, Amravati, India.

Email: sachin.khanande46@gmail.com

#### 1. INTRODUCTION

An adaptive filter is a computational device that attempt to model the relational device between two signals in real time environment in an iterative manner. Adaptive filter are often realise either as a set of program instruction running on an arithmetical processing device such as microprocessor or DSP (digital signal processor) chip or as set of logic operation implemented in FPGA or in semicustom or custom VLSI circuit however ignoring any error introduced by numerical precision effect. In this implementation, the fundamental operation of an adaptive filter can be characterised independently of specific physical realization that it take. For this reason proposed method focuses on their specific realization in software and hardware [1-3].

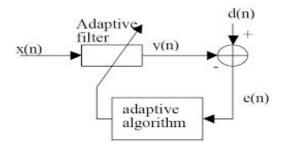

The demand and popularity of portable electronics is driving designers make great efforts to achieve for small silicon area, higher speeds, and power dissipation and reliability. The proposed work deals with the design and performance analysis of Adaptive Filter in VLSI. Figure 1 shows the basic concept of the adaptive filter which uses Least Mean Square Algorithm for minimizing the error [4-5].

210 ☐ ISSN: 2089-4864

Figure 1. Generalized structure of adaptive filters

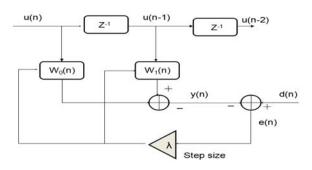

The disadvantage of LMS algorithm is that, it cannot meet the requirement of fast rate of convergence and minimum MSE. The best choice is to use the block recursive least squares (RLS) algorithm to overcome the above difficulty. Block Recursive Least Square-DCD (Dichotomous Coordinate Decent) algorithms are known to exhibit better performances. And is one of the variants algorithm in which the updating of weights is done at block level and the error values are calculated at every clock cycle. The weights are updated once per every block data instead of updating on every clock cycle of input data. The error values are calculated at every clock cycle [6-9]. Figure 2 RLS adaptive filter shows u (n) is the input and y (n) is the output of the filter. d (n) desired response of Adaptive filter Error denoted by e(n) this error is subtract with filter output and desired output i.e. e(n) = y(n)-d(n) and it's called as estimation error. The aim of this filtration is to remove the estimation error.  $\lambda$  is step-size which is used for adaptation of the weight vector, the tap-weight vector w(n) and the tap-input vector u(n) is defined as follows

$$\begin{split} W(n) &= [w_0(n), wI(n), ..., wn_{-l}(n)]^T \\ u(n) &= [u(n), u(n-1), ..., u(n-N+1)]^T \\ k(n) &= \frac{\lambda^{-1}P(n-1)u(n)}{1+\lambda^{-1}u^H(n)P(n-1)u(n)} \\ &\quad \xi(n) = d(n) - \bigwedge^{\wedge}(n-1)u(n) \\ &\quad \hat{w}(n) = \bigwedge^{\wedge}(n-1) + k(n)\xi^*(n) \\ P(n) &= \lambda^{-1}P(n-1) - \lambda^{-1}k(n)u^H(n)P(n-1) \;. \end{split}$$

Figure 2. RLS Adaptive filter

The Z-inverse is a delay element used for controlling the input of filter. Whenever the first input is given to the filter u(n) at that time other input have stand-by condition then second input are given to filter that is u(n-1) at a time many inputs not process becouse of delay. The proposed dissertation work deals with the design of simple architecture for the implementation of a variant of Block DCD RLS-algorithm where the weight updating and error calculation are both calculated in block wise fashion.

#### 2. RELATED WORK

Adaptive filter is forms the important basis for many real time digital signal processing applications. Many researchers have worked on adaptive filters for various diverse applications. The detail literature survey for the proposed dissertation is as follows:

The Important work is carried out by Jafar Saniie et al., in which author proposed the Hardware and Software Design for QR Decomposition Recursive Least Square Algorithm. An embedded hardware and software system was design and implementation for QR Decomposition Recursive Least Square (QRD-RLS) algorithm using Given's Rotation method for optimizing the area and power [1].

Dr. C. Vijaykumar et al. presented one of most important implementation of low power systolic base adaptive filter by deigning the RLS Adaptive Filter architecture using FPGA technology with clock getting. Systolic array architecture were used to reduce the circuit scale into half without impairing the processing speed and clock gating which results in the considerable reduction in power[2].

Md. Zulfiquar Ali et al., author suggest the New Improved Recursive Least-Square Adaptive-Filtering Algorithms. In this paper two new improved recursive least-squares adaptive-filtering algorithms, one with a variable forgetting factor and the other with a variable convergence factor are proposed. Optimal forgetting and convergence factors are obtained by minimizing the mean square of the noise-free a posterior error signal [3].

Author Cristian Stanciul et al., says that in Numerical Properties of the DCD-RLS Algorithm for Stereo Acoustic Echo Cancellation, Modern teleconferencing systems have been developed in recent years to use multiple acoustic channels (stereo communication). This feature improves the quality of Communication (e.g., in terms of spatial localization), but the classic problem of the acoustic echo cancellation becomes more complicated. In this context, the dichotomous coordinate descent (DCD) - recursive least-squares (RLS) algorithm can be an attractive choice for hardware implementation [5].

Other work carried by Yuriy Zakharovt, et al., in which Fast RLS algorithm using dichotomous coordinate descent iterations in this the Recursive Least Squares (RLS) adaptive filtering problem is expressed in terms of auxiliary normal equations with respect to increments of the filter weights. By applying this approach to the exponentially weighted case, a new structure of the RLS algorithm is derived. For solving the auxiliary equations, dichotomous coordinate descent (DCD) iterations with no explicit division and multiplication are used [8].

From the review of various papers, it is found that DCD algorithm is used for minimizing the iteration with greater speed and it can be very useful for Hardware implementation also. Existing methods is base on matrix inversion problem. However, the proposed method can be used to overcome the problem of matrix inversion by using Block DCD-RLS algorithm.

## 3. CONCLUSION

Adaptive filtering techniques can be used in many applications in different fields, such as wireless communication and channel equalization, noise cancelling, channel estimation.

The serial implementation of the real-valued Block DCD algorithm will be the smallest hardware implementation and it is notable for smaller than any other methods requiring multiplication operations. However, the update rate is limited as the residual vector is updated sequentially.

#### REFERENCES

- [1] Sufeng Niu Sizhou, Wang Aslan, S. Saniie J, "Hardware and Software Design for QRD decomposition Recursive Least Square Algorithm", *Department of Electrical and Computer Engineering IEEE*, 2013, pp. 978-982.

- [2] Marjan Karkooti, Joseph R. Cavallaro, "FPGA Implementation of Matrix Inversion Using QRD-RLS Algorithm," 2005 IEEE, pp. 1625-1629.

- [3] Md. Zulfiquar Ali Bhotto, and Andreas Antoniou, "New Improved Recursive Least-Squares Adaptive-Filtering Algorithms," *IEEE Transactions on Circuits and Systems—I: Regular Papers*, June 2013, Vol. 60, No. 6, pp. 1549-1557.

- [4] Reza Arablouei, Kutluyıl Doğançay, and Tülay Adal, "Unbiased Recursive Least-Squares Estimation Utilizing Dichotomous Coordinate-Descent Iterations," *IEEE transactions on signal processing*, Vol. 62, No. 11, June 1, 2014, pp 1053-587.

- [5] Cristian Stanciu and Cristian Anghel, "Numerical Properties of the DCD-RLS Algorithm for Stereo Acoustic Echo Cancellation," *IEEE*, 2014, pp. 978-781.

- [6] Juan Paulo Robles Balestero, Fernando Lessa Tofoli, Grover Victor Torrico-Bascop'e, "Active Online System Identification of Switch Mode DC–DC Power Converter Based on Efficient Recursive DCD-IIR Adaptive Filter," IEEE Transactions on Power Electronics, Vol. 27, No. 11, November 2012, pp. 0885-8993.

- [7] Jie Liu; Zakharov, Y, "FPGA implementation of RLS adaptive filters using dichotomous coordinate descent iterations," *IEEE International Conference IEEE*, 2009, pp. 978-982.

212 ISSN: 2089-4864

[8] Yuriy Zakharovt, George White and Jie Liut, "Fast RLS algorithm using dichotomous coordinate descent iterations," *Conference Record of the Forty-First Asilomar Conference on 2007 IEEE*, 4-7 Nov. 2007,pp 431-435.

[9] Purushothaman A and Dr. C. Vijaykumar, "Implementation of Low power systolic based RLS adaptive Filter using FPGA"