# Effect of integrated power and clock networks on combinational circuits

#### Rajeshwari Bhat<sup>1</sup>, Mohammad Rashid Ansari<sup>2</sup>, Ruqaiya Khanam<sup>3</sup>

<sup>1,2</sup>Electronics and Communication Engineering Department, Galgotias University, Greater Noida, India <sup>3</sup>Electronics and Communication Engineering Department, Sharda University, Greater Noida, India

# Article Info ABSTRACT

### Article history:

Received Jun 28, 2020 Revised Aug 25, 2020 Accepted Oct 8, 2020

#### Keywords:

Clock network Combinational circuits Gates Inverter Power efficiency Sequential circuits Reduction of power consumption is necessary in a system on chip. To achieve this, power and clock networks can be integrated. This leads to a significant reduction in power consumption in a circuit. This paper explores the effect of such a network on various combinational circuits and compares the power consumption of these circuits with conventional combinational circuits. The combinational circuits which are powered by the proposed circuit consume lesser power as compared to conventional combinational circuits.

This is an open access article under the <u>CC BY-SA</u> license.

# Corresponding Author:

Rajeshwari Bhat, Electronics and Communication Engineering Department, Galgotias University, Sector 17A, Greater Noida, Uttar Pradesh 203201, India. Email: rajeshwaribhat2@gmail.com

# 1. INTRODUCTION

As integrated circuits become more complex, the power consumption increases and the performance also increases. The continuous scaling of transistors and the increase in their frequency of operation has led to an increase in the overall power consumption of the chip. This increase in the complexity of the chip, in accordance with the Moore's Law, has also led to increased power densities within the Integrated circuit. A primary consumer of power on-chip is the Clock Distribution Network or the Clock Tree. Traditionally, it wa consumes anywhere between 30% to 50 % of the total dynamic power [1-5].

Complex integrated circuits have higher performance and lower power utilisation. With limited onchip resources circuit designing becomes a complex task. These resources are majorly used by the three main lines of clock, ground and power in a IC. Characteristics of a circuit differ from one another and the net result is heavy utilisation of existing on-chip resources [6-8].

With limited on-chip resources it becomes necessary to design circuits which reduce the power consumption. One such circuit is an integrated power and clock distribution circuit which reduces power consumption significantly by around 60% The effectiveness of this designed circuit has been tested on various combinational circuits [9-15].

The research articles which have been published on GIPAC [1] include various methods for decreasing energy usage in circuits. Earlier literature had tried merging power and clock signals throughout the chip. The combined signals were filtered and two signals were obtained from the GIPAC [1] network.

Higher frequency signal is the clock signal and the signal with a constant dc value is Vcc or the power signal. Hence filtering the signals into two separate components is plausible.

Another literary work explores the possibility of eliminaing the whole CDN [2], totally by merging the two networks. Newer literature on combinatorial wire-wireless clock distribution networks [3] suggests a combined circuit consisting of wired and wireless clock networks. Here circuits were designed using transmitters and receivers, and generated a clock signal which was wireless in nature. The circuit used On-Off-Keying (OOK) transceivers[3] which were used for reduction in propagation delay , increase power eficiency and reduce the complexity of the circuit. This circuit had a propogation delay lower than a normal clock circuit. The circuit also had a reduced clock skew [16-21].

The research articles which have been published on GIPAC [1] include various methods for decreasing energy usage in circuits. Earlier literature had tried merging power and clock signals throughout the chip. The combined signals were filtered and two signals were obtained from the GIPAC [1] network. Higher frequency signal is the clock signal and the signal with a constant dc value is Vcc or the power signal. Hence filtering the signals into two separate components is plausible.

Another literary work explores the possibility of eliminaing the whole CDN[2], totally by merging the two networks. As the clock network consists of a clock grid driven by a global h-tree, the metal lines implemented both horizontally and vertically would require atleast four metal layers. If a similar power network is considered throughout the chip then a total of 6 metal layers would be used [22-25].

If the clock and power networks were to be merged then a total of four metal layers would be required thus saving two metal layers. Comparing typical resonant networks with these circuits, a signal generated by this circuit has a swing of 400 mV around Vdc. The usual resonant clock networks [11] generate a full swing clock signal from 0 to  $V_{DD}$

The output of the IPCDN [2] circuit can be directly connected to the power line of the entire circuit. This helps to eliminate local clock networks [9] and also the use of filter circuits. Also, the voltage swing of 400mV for the generated signa it is quite low as compared to the traditional clock networks. But in a IPCDN [2] circuit needs a clock buffer to convert the generated signal into a full swing clock signal, which is necessary to operate the sequential circuits.

Newer literature on combinatorial wire-wireless clock distribution networks [3] suggests a combined circuit consisting of wired and wireless clock networks. Here circuits were designed using transmitters and receivers, and generated a clock signal which was wireless in nature. The circuit used On-Off-Keying (OOK) transceivers [3] which were used for reduction in propagation delay , increase power efficiency and reduce the complexity of the circuit. This circuit had a propogation delay lower than a normal clock circuit. The circuit also had a reduced clock skew.

# 2. RESEARCH METHOD

This paper explores a CMOS oscillator circuit which generates a combined signal used to run a combinational circuits. The designed circuit was tested on a inverter. NAND and a NOR gate for its effectiveness.

The designed circuit is a transistor based CMOS oscillator circuit and when simulated, the circuit [12] generates a 415mV swing. The generated signal is the *pwr\_clk* signal and has a dc component alongwith a sinusoidal swing. The generated signal can be directly connected to run a Inverter, NAND and a NOR gate.

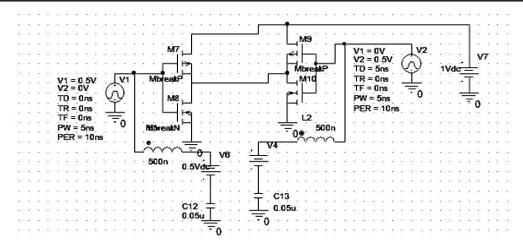

The designed circuit can be used to integrate power and clock network signals and can be used to drive the digital part of a chip, as analog part of the circuit is vulnerable to fluctuations in the power supply. The proposed circuit is as shown in Figure 1. The signals generated are of opposing polarity to each other.

The generated *pwr\_clk* signal can be connected directly to run a Inverter, NAND and NOR gate, but to connect to a sequential circuit, a full swing clock signal is necessary and this calls for a clock buffer circuit.

Figure 1. Proposed CMOS oscillator circuit

#### 3. RESULTS AND DISCUSSION

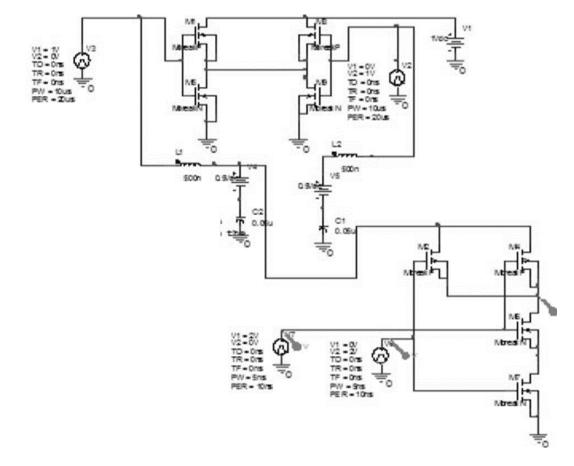

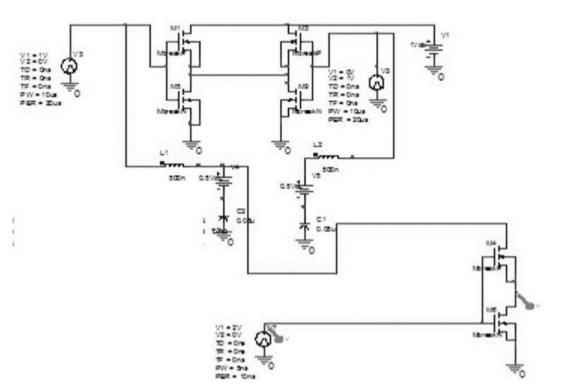

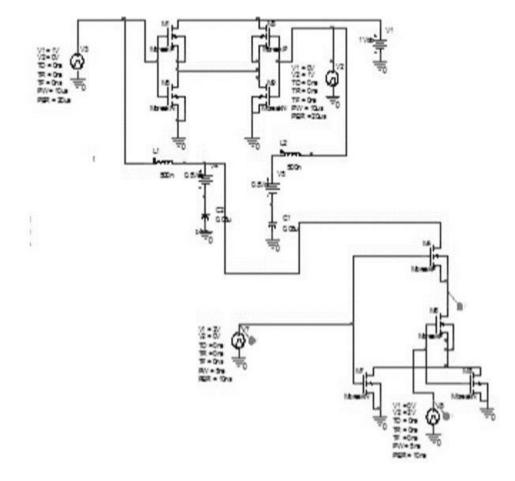

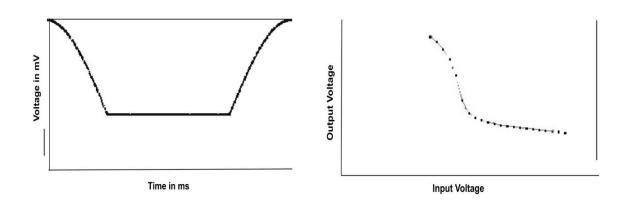

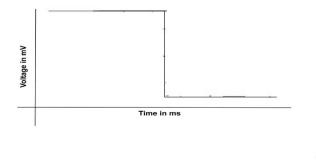

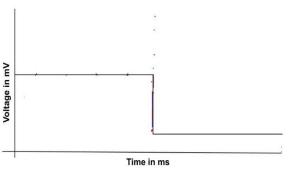

To simulate the designed circuit, SPICE CIS lite version 17.2 was used. The simulation results show the circuit of a CMOS oscillator implemented on a NAND gate as shown in Figure 2. The CMOS oscillator implementation on a inverter circuit is shown in Figure 3. Figure 4 shows the implementation of a CMOS oscillator circuit on a NOR gate. Figure 5 shows the simulation output for a NAND gate. The Voltage transfer characteristics of a inverter implemented with a CMOS oscillator is shown in Figure 6. Simulation output of a Inverter with a CMOS oscillator is shown in Figure 7. Figure 8 shows the simulation output of a NOR gate.

Figure 2. CMOS oscillator circuit with a NAND gate

Figure 3. CMOS oscillator with a inverter

Figure 4. CMOS oscillator with a NOR gate

Effect of integrated power and clock networks on combinational circuits (Rajeshwari Bhat)

Figure 5. Simulation output for NAND gate

Figure 6. VTC characteristics of inverter with CMOS oscillator

Figure 7 Simulation output of inverter with IPCDN

Figure 8. Simulation output of NOR gate with IPCDN

Table 1 shows the comparison of Voltage swing for GIPAC, IPCDN circuit and the designed CMOS oscillator circuit. Table 2 shows the comparison for power dissipation and transistor count for IPCDN and designed CMOS oscillator circuit. Table 3 shows comparison of power consumption for inverter with CMOS oscillator circuit and a typical inverter circuit. Table 4 shows comparison of power consumption in NAND gate with CMOS oscillator and a normal NAND gate. Table 5 shows comparison of power consumption in NOR gate with and without the CMOS oscillator circuit.

| Table 1. Comparison of voltage swing for various methods |                         |                    |                        |  |

|----------------------------------------------------------|-------------------------|--------------------|------------------------|--|

| Sl.No                                                    | Methods                 | Voltage swing (mV) | Supply Voltage Vdd (V) |  |

| 1                                                        | GIPAC [1]               | 100                | 1.2                    |  |

| 2                                                        | IPCDN [2]               | 400                | 1                      |  |

| 3                                                        | CMOS Oscillator circuit | 415                | 1                      |  |

|               | • •        |         | 4           | 1   | · · ·            |

|---------------|------------|---------|-------------|-----|------------------|

| Table 7 Com   | naricon to | r nowar | discingtion | and | transistor count |

| 1 auto 2.0011 | Dalison tu |         | uissibauon  | anu | transistor count |

|               |            |         |             |     |                  |

| Sl.No | Methods                 | Power dissipation in µW | No. of transistors |

|-------|-------------------------|-------------------------|--------------------|

| 1     | IPCDN [2]               | 6.4                     | 18                 |

| 2     | CMOS Oscillator circuit | 2.5                     | 10                 |

| Table 3. | Comparison of | power consumptio | n for inverter |

|----------|---------------|------------------|----------------|

|----------|---------------|------------------|----------------|

| Sl.No | Power consumed by inverter with CMOS Oscillator in $\mu w$ | Power consumption in a normal Inverter in $\mu w$ |

|-------|------------------------------------------------------------|---------------------------------------------------|

| 1     | 73.51                                                      | 200                                               |

Table 4. Comparison of power consumption in NAND gate

| Sl.No | Power consumed by NAND gate with CMOS oscillator in fW | Power consumption in a normal NAND gate in fW |

|-------|--------------------------------------------------------|-----------------------------------------------|

| 1     | 550                                                    | 5000                                          |

Table 5. Comparison of power consumption in NOR gate.

| Sl.No | Power consumed by NOR gate with CMOS oscillator in pW | Power consumption in a normal NOR gate in pW |

|-------|-------------------------------------------------------|----------------------------------------------|

| 1     | 3                                                     | 1790                                         |

#### 4. CONCLUSION

In this paper, the proposed circuit have successfully designed to generate a combined signal. Results of simulation show signals upto 5 GHz an be generated. Implemented circuit has been tested on combinational circuits like Inverter, NAND and NOR gate and it is found that these gates consume 10 times lesser power with the proposed circuit as compared to conventional NAND, NOR and NOT gates.

#### REFERENCES

- [1] R. Jakushokas and E. G. Friedman, "Globally integrated power and clock distribution network," *Proceedings of 2010 IEEE International Symposium on Circuits and Systems*, pp. 1751–1754, 2010.

- [2] Seyed E. Esmaeili and Asim J. Al-Kahlili, "Integrated power and clock distribution network," *IEEE Transactions on Very Large Scale Integration (VLSI) SYSTEMS*, vol. 21, no. 10, pp. 1941-1945, Oct 2013,

- [3] Qian Ding, Benjamin J. Fletcher, and Terrence Mak, "Globally wireless locally wired (GloWiLoW): A clock distribution network for many-core systems," In 2018 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-5, 2018.

- [4] V. F. Pavlidis, I. Savidis, and E. G. Friedman, "Clock distribution networks in 3-D integrated systems," *IEEE Trans. Very Large S cale Integr. (VLSI) Syst.*, vol. 19, no. 12, pp. 2256–2266, Dec. 2011.

- [5] Wolfgang M. Arden, "The International Technology Roadmap for Semiconductors—Perspectives and challenges for the next 15 years," *Current Opinion in Solid State and Materials Science*, vol. 6, no. 5, pp. 371-377, 2002.

- [6] S. M. Kang and Y. Leblebici, CMOS digital integrated circuits, 3rd ed. New York: McGraw-Hill, pp. 260–263, 2003.

- [7] M. Popovich, A. V. Mezhiba, and E. G. Friedman, *Power distribution networks with on-chip decoupling capacitors*, New York: Springer Science & Business Media, 2008.

- [8] International Technology Roadmap for Semiconductors, 2007. [Online]. Available: http://www.itrs2.net/

- [9] E. G. Friedman, "Clock distribution networks in synchronous digital integrated circuits," *Proceedings of the IEEE*, vol. 89, no. 5, pp. 665–692, May 2001.

- [10] K. L. Wong, T. Rahal-Arabi, M. Ma, and G. Taylor, "Enhancing microprocessor immunity to power supply noise with clock-data compensation," *IEEE Journal of Solid-State Circuits*, vol. 41, no. 4, pp. 749–758, Apr 2006.

- [11] S. E. Esmaeili, A. J. Al-Khalili, and G. E. R. Cowan, "Estimating required driver strength in the resonant clock generator," in *Proc. IEEE Asia Pacific Conf. Circuits Syst.*, pp. 927–930, Dec. 2010

- [12] Rajeshwari Bhat and Ruqaiya khanam "Integrated power and clock distribution circuits in a wired and wireless clock network," *International Journal of Innovative Technology and Exploring Engineering (IJITEE)*, vol. 8, no. 7S, pp. 154-157, May 2019

- [13] M. S. Supreeth, D. Jennifer Judy, Kore Sagar and V. S. Kanchana Bhaaskaran, "Low power energy recovery clock," *International Conference on Communications and Signal Processing (ICCSP)*, pp. 877-881, Apr 2014.

- [14] Jennifer Judy Dominic Jawahar, Supreeth Mysore Shivananda Murthy and Kanchana Bhaaskaran Vettuvanam Somasundaram, "Self-gated resonant-clocked flip-flop optimized for power efficiency and signal integrity," *IET Circuits, Devices & Systems*, vol. 2, no. 10, pp. 94-103, Apr 2016.

- [15] T. Eudes, B. Ravelo and A. Louis, "Experimental validations of a simple PCB interconnect model for high-rate signal integrity," *Trans. Electromagn. Compat.*, vol. 54, no. 2, pp. 397-404, 2012.

- [16] T. Hirano, K. Okada, J. Hirokawa et al., "Electromagnetic simulation modeling of silicon substrate for 60 GHz onchip differential-feed dipole antenna," *Appl. Phys. Lett.*, vol. 103, no. 12, pp. 122101, 2013.

- [17] A. Chattopadhyay and Z. Zilic, "Flexible and reconfigurable mismatch-tolerant serial clock distribution networks," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 20, no. 3, pp. 523-536, Mar 2012.

- [18] H. Zhu and V. Kursun, "Novel low-leakage and high-speed triple-threshold-voltage buffers with skewed inputs and outputs," *IEEE Transactions on Circuits and Systems I*, vol. 61, no. 7, pp. 2013-2021, Jul 2014

- [19] V. F. Pavlidis, I. Savidis and E. G. Friedman, "Clock distribution networks in 3-D integrated systems," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 19, no. 12, pp. 2256-2266, Dec 2011.

- [20] Q. Fan and N. Ansari, "Application aware workload allocation for edge computing-based IoT," *IEEE Internet of Things Journal*, vol. 5, no. 3, pp. 2146-2153, Jun 2018.

- [21] H. Zhu and V. Kursun, "2-Phase high-frequency clock distribution with SPLIT-IO dual-Vt repeaters for suppressed leakage currents," *IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 2932-2935, May 2015.

- [22] A. K. Gundu and V. Kursun, "Low leakage clock tree with dual-threshold-voltage split input-output repeaters", *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 7, pp. 1-11, Mar 2019.

- [23] M. R. Guthaus, "Distributed LC resonant clock tree synthesis," Proceedings of the IEEE International Symposium on Circuits and Systems, pp. 1215-1218, May 2011.

- [24] M. Buttrick and S. Kundu, "On testing pre-bond dies with incomplete clock networks in a 3D IC using DLLs," *Proceedings of the Conference on Design, Automation and Test in Europe*, pp. 14-18, Mar 2011.

- [25] 2011 International Technology Roadmap for Semiconductors (ITRS), 2011. [Online]. Available: https://www.semiconductors.org/resources/2011-international-technology-roadmap-for-semiconductors-itrs/

#### **BIOGRAPHIES OF AUTHORS**

Rajeshwari Bhat, the author of this paper is an M.Tech in VLSI Design and is presently persuing her PhD program at Galgotia University, Greater Noida. She has already published a paper titled "Integrated Power and Clock Distribution Circuits in a Wired and Wireless Clock Network " in IJITEE in May 2019

Dr. Mohammad Rashid Ansari, earned his B.Tech., from, AMU, Aligarh in 2001, M.Tech. (Digital Systems), from MNNIT, Allahabad, in the year 2003 and completed his Ph.D. from Jamia Millia Islamia (A Central University) in 2019. He is currently working as Faculty member in Department of ECE in SEECE, Galgotias University. He has published several research papers in various International Journals and International/National conferences, has also attended several national and international conferences and workshops.

He was technical committee members of many international conferences, including ICEEE2020, RDCAPE2019, NANOfIM2017, GUCON 2019. He has received best paper award in INDICON 2015. He is a member of IEEE.

Ruqaiya Khanam received the B.Tech degree in Electronics and Communication from the University of Jamia Millia Islamia, Delhi, India in 1998 and M.Tech degree in Electronic Circuit and System Design from Aligarh Muslim University, Aligarh, India in 2004. She received the PhD degree in Electronics and Communication from Jamia Millia Islamia, Delhi, India in 2014. She is with Electronics and Communication Engineering Department, Sharda University, Greater Noida, India, where she is currently a Professor. Her current research interests include VLSI design and technology, high level designing using VHDL/Verilog, low Power Chip Designing, image Processing, biomedical signal and image processing, fuzzy logic processor design and internet of things.