# Two state-of-the-arts current-mode ternary full adders based on CNTFET technology

Mona Moradi Roudehen Branch, Islamic Azad University, Iran Email: mo.moradi@riau.ac.ir

## **Article Info**

# Article history:

Received Apr 16, 2019 Revised Oct 7, 2019 Accepted Nov 12, 2019

## Keywords:

CNTFET Current mode logic MVL circuitry Ternary full adder

## ABSTRACT

Adder core respecting to its various applications in VLSI circuits and systems is considered as the most critical building block in microprocessors, digital signal processors and arithmetic operations. Novel designs of a low power and complexity Current Mode 1-bit Full Adder cell based on CNTFET technology has been presented in this paper. Three major parts construct their structures; 1) the first part that converts current to voltage; 2) threshold detectors (TD); and 3) parallel paths to convey the output currents flow. Adjusting threshold voltages which are significant factor for setting threshold detectors switching point has been achieved by means of CNTFET technology. It would bring significant improvements in adjusting threshold voltages, regarding to its unique characterizations. Simple design, less transistor counts and static power dissipation and better performance comparing previous designs could be considered as some advantages of the novel designs.

This is an open access article under the <u>CC BY-SA</u> license.

## Corresponding Author:

Mona Moradi, Roudehen Branch, Islamic Azad University, PO Box: 189, Roudehen, Tehran, IR Iran. Email: mo.moradi@riau.ac.ir

# 1. INTRODUCTION

In Current Mode Logic (CML), logical levels are represented by currents. This approach has its own pros and cons compared to the conventional Voltage Mode Logic (VML). The merits include: 1) the reduction of the number of active devices in a circuit by means of a simple wiring procedure [1]; 2) the ease of circuit development and producing several multiple-input circuits by using different Threshold Detectors (TDs) [2]; 3) the elimination of sign bit by applying the direction of current to describe the sign [1]; 4) less noise sensitivity [3, 4]; 5) the usage of current mirrors for current scaling and duplication [4, 5]; and 6) high-speed operation [4, 5]. The main disadvantage of CML is its high static power consumption [5, 6]. Regarding the requirement of higher speed, it is expected that current mode approaches become even more important in near future [6, 7].

Traditionally, bipolar and MOS devices have been utilized to implement current mode circuits. The latter is often selected for mixed analog-digital signal environments. Meanwhile, MOSFETs benefit from higher supply noise immunity [3-6], and less power consumption.

Multiple-Valued Logic (MVL) approach uses more than two logic levels. It relies on the increment of logic levels, whereas Binary logic computations are based on only two values ('0' and '1'). MVL benefits from fewer interconnections and pinouts, less area dissipation, and higher parallel and serial communication rates [1]. These advantages with regards to the serious challenges of interconnections and the amount of wire congestion in nanoscale chips, make MVL as an alternative design technique for Binary circuits [5, 6].

19

In short, MVL is a mixture of binary logic and analogue signal processing. It takes advantage of both noise tolerance of a digital signal and more information processing in analogue mode [8]. Among different MVL systems, Ternary logic brings about less product cost and complexity comparing to Binary logic [8-11].

Voltage-mode MVL circuits suffer from the reduction of voltage swing during encoding more than two logic levels [12]. The current-mode technique seems to be a possible solution to overcome the challenge. This approach utilizes current as a signal carrier, either alone or in mixture with voltage [12]. Regarding the design simplicity and less noise sensitivity, the current mode approach can be considered as a worthy technique for designing MVL circuits [12-14].

For many years, MOSFET technology has been considered as the premier technology, providing the vital potentials to implement energy-efficient and dense VLSI circuits. However, the trend of scaling down the feature size of CMOS technology in nano-ranges in today's nanometer VLSI industry leads to numerous challenges. Carbon NanoTube Field Effect Transistor (CNTFET) [15], owing to its unique specifications and the ability of adjusting the desired threshold voltage, has achieved considerable attention as a successor to the MOS technology in near future, especially for MVL designs.

This paper presents new Ternary Full Adder cells. They are based on CNTFET technology and CML design approach. Full Adder is considered as the most important component [16-18] because of its consequential role in digital signal processors, microprocessors, and arithmetic operations and computations. Therefore, its efficiency impacts the performance of a system as a whole [16, 17]. The new proposed circuits are built on mixed current and voltage signals. A constant current source is applied respecting to the logical relationship between the sum of input currents and constant current value. Hence, power dissipation is reduced in comparison with the previously presented structures.

The rest of the paper is organized as follows: Section 2 reviews the previously presented currentmode Ternary Full Adders in the literature and their transistor-level implementation will be presented. The proposed designs are presented in Section 3. Simulation results and comparisons are accessible in Section 4. Finally, section 5 draws the conclusion.

#### 2. LITERATURE REVIEW

Full Adder can be used in MVL systems either in CML or VML mode, based on both MOSFET and CNTFET technologies [10, 12, 13]. Nevertheless, CNTFET-based adders provide higher performance [19-21]. Some current-mode Full Adders have been presented previously in [22-24] based on linear addition and subtraction of input currents. Their design simplicity can be considered as their major advantage. The presented CML Full Adder in [22] is specifically designed for fuzzy logic. In discrete systems and circuits the ability of generating full-swing outputs, even with non-full-swing input signals, is one of the essential characteristics. Fuzzy circuits do not provide this vital necessity. Their employment in digital systems most probably causes some problems such as malfunction and high noise sensitivity [5, 6].

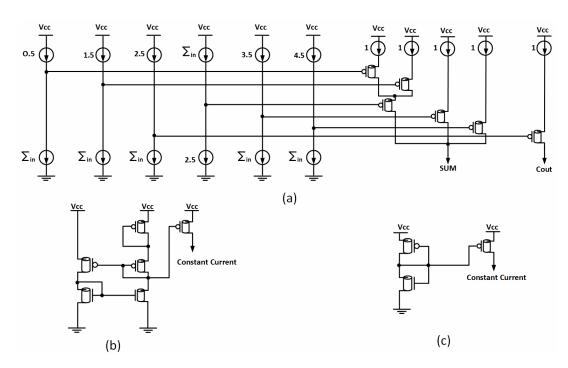

Figure 1a display the first prior Ternary Full Adder circuit, presented in [24]. A threshold detector is implemented by using a constant independent current source whose function depends on which network it is situated:

- If the constant independent current source is placed in a pull-up network: In this case, whenever the sum of input currents (Σin) is less than a constant value (the threshold), the relevant p-type transistor turns off, since the rest of the current charges the gate capacitor of the p-type transistor.

- If the constant independent current source is placed in a pull-down network: The related p-type transistor switches on if the sum of input currents ( $\Sigma$ in) is more than a constant value (the threshold).

The transistor-level implementations of a constant independent current source are exhibited in Figures 1b and 1c [23, 25]. Both implementations are used in this paper. The three positive logic values  $\{0, 1, 2\}_3$  explain the unsigned Ternary digits. They are characterized in current-mode logic by different current levels. Each current unit is considered as  $8\mu$ A. Therefore, logical values '0', '1', and '2' are equivalent to 0A,  $8\mu$ A, and  $16\mu$ A, respectively.

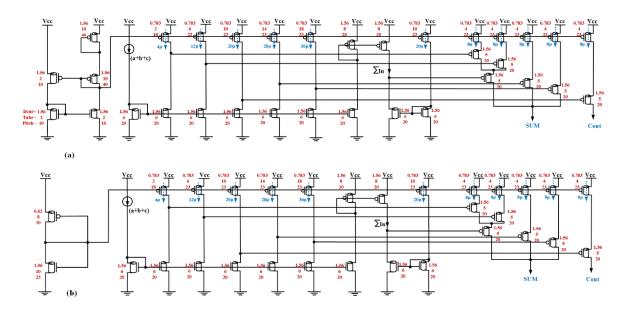

Figure 2 depicted the transistor-level implementations of the former Ternary Full Adder by two different constant independent current sources. Each transistor is marked by three values (numbers), which indicate the diameter of CNTs ( $D_{CNT}$ ), the number of nanotubes under the gate terminal (Tube), and the pitch parameter. For example, a transistor with the values 0.783, 6, and 18 has two CNTs with the diameter of 0.783nm under its gate terminal. Therefore, its threshold voltage is 0.549V (1) [19-21]. Meanwhile, the distance between the centers of two adjacent CNTs is 18nm (Pitch=18nm). In addition, these designs need constant currents of 4 $\mu$ A, 8 $\mu$ A, 12 $\mu$ A, 20 $\mu$ A, 28 $\mu$ A, and 36 $\mu$ A as threshold detectors. Furthermore, current mirror circuits are used to duplicate the sum of input value currents ( $\Sigma$ in).

Figure 1. The previously presented circuits; (a) Ternary full adder [24], (b) independent current source [25], (c) Constant independent current source [23]

Figure 2. The previous current-mode circuits [24]; (a) with independent current source [25], (b) independent current source [23]

# 3. THE PROPOSED CURRENT-MODE TERNARY FULL ADDER (CMTFA)

In this section, it is explained the results of research and at the same time is given the comprehensive discussion. Results can be presented in figures, graphs, tables and others that make the reader understand easily [2, 5]. The discussion can be made in several sub-chapters.

Two state-of-the-arts current-mode ternary full adders based on CNTFET technology (Mona Moradi)

**D** 21

Full Adder cells are principally considered among the most fundamental logic blocks. Respecting to their numerous applications in other mathematical operations, they could be used in many large and complex circuits and functional units such as multiplier and ALU [26, 27]. Table 1 shows the functionality of a current mode Ternary logic Full Adder based on its inputs summation. New Ternary Full Adder circuits based on CML and CNTFET technology are proposed separately in this section. They both exploit Multiple-Valued Current Mode Logic (MVCML) specifications [1, 6, 9] and the unique characteristics of CNTFET technology [19-21] like its flexibility in MVCML. Their designing method relies on converting the sum of the input currents to voltage. The switching activity of the final transistors is controlled by threshold detectors, which are located through the output paths. A unit of current flows if an output transistor switches on. Accordingly, the currents of two different paths are summed up to increase the amount of current to  $16\mu$ A.

| Table 1. The truth table of ternary full adder |      |     |  |  |

|------------------------------------------------|------|-----|--|--|

| $\Sigma in(a, b, C_{in})$                      | Cout | SUM |  |  |

| 0                                              | 0    | 0   |  |  |

| 1                                              | 0    | 1   |  |  |

| 2                                              | 0    | 2   |  |  |

| 3                                              | 1    | 0   |  |  |

| 4                                              | 1    | 1   |  |  |

| 5                                              | 1    | 2   |  |  |

| 6                                              | 2    | 0   |  |  |

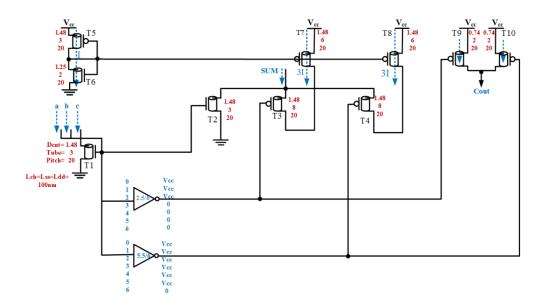

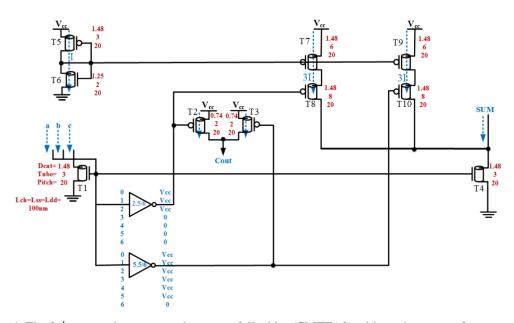

Figures 3 and 4 demonstrate the 1<sup>st</sup> and 2<sup>nd</sup> proposed CML Ternary Full Adder cells. A Full Adder cell includes three inputs (a, b and  $C_{in}$ ) and two outputs (SUM and  $C_{out}$ ). The presented technique is founded upon the sum of input currents. In CML, the simple connection of input wires provides the linear addition of inputs. In order to convert the sum of the input currents ( $\Sigma$ in) to voltage, a diode-connected transistor ( $T_1$ ) is used as a resistor. To achieve higher resistivity, the channel ( $L_g$ ) and doped CNT source- ( $L_{ss}$ ) and drain-side ( $L_{dd}$ ) extension regions have been stretched to 100nm. Although the channel length increment makes more resistance, it does not decrease the operation speed, since the converting transistors do not impact the critical path of the whole cell [5, 7].

After the conversion, the threshold detectors (TDs) are responsible for controlling the switching activity of the rest of the transistors [5]. As mentioned earlier, the threshold value adjustment is accomplished by changing the diameter of CNTs (1) [19-21].

Both proposed structures include a constant current source, which is responsible for generating a constant current value.  $T_5$  and  $T_6$  are used for this purpose. In (2) explains the way the output Sum is generated.

$$Sum = \Sigma in - 3I_1 - 3I_2 \tag{2}$$

The proposed Ternary Full Adder design uses two TDs, whose turning points are set as follows: For example, the output of the TD with switching point of  $\frac{5.5}{6}$  would be equivalent to '0', if the summation of inputs (a, b, C<sub>in</sub>) equals to ( $\Sigma$ in=6) as shown in Figures 3 and 4. The presented Adder Cells do not need binary inverter, which leads to better performance.

The last part is the most important part of this structure. It defines the output values (SUM and  $C_{out}$ ). It contains of different paths, through which the output currents flow. It is necessary to set the dimensions of the transistor(s) on a specific path properly. This leads to the precise unit of output current (0, 8µA, and 16µA).

Over and above, two parallel paths constructed by two transistors in each path  $T_3$ ,  $T_7$  and  $T_4$ ,  $T_8$  are used to generate SUM based on (2). However,  $T_2$  directs the current of input summation ( $\Sigma$ in). For Sum output, the current through the paths, including  $T_7$ ,  $T_3$  and  $T_8$ ,  $T_4$  would flow, based on TDs switching point and their related transistors. Transistors  $T_9$  and  $T_{10}$  generate Cout values based on their switching status as shown in Figure 3.

The switching points of TDs are set properly so that  $T_3$  and  $T_9$  are switched on if  $\Sigma$ in>3 and  $T_4$ ,  $T_{10}$  are switched on if  $\Sigma$ in>6(Figure 3).

The main functionality of the presented cells is as follows (Figure 3):

If the sum of the inputs equal to '0', transistors  $T_3$ ,  $T_4$ ,  $T_9$ , and  $T_{10}$  are switched off; accordingly both outputs would equal 0.

Int J Reconfigurable & Embedded Syst, Vol. 9, No. 1, March 2020: 19-27

In case of ( $\Sigma$ in=1), T<sub>3</sub>, T<sub>4</sub>, T<sub>9</sub>, and T<sub>10</sub> are switched off, while T<sub>2</sub> would be switched on. It copies the summation of input currents, so the 8µA current to the SUM output would be indicated, although C<sub>out</sub> equals 0.

While ( $\Sigma$ in=2), the threshold detector switches T<sub>3</sub>, T<sub>4</sub>, T<sub>9</sub>, and T<sub>10</sub> are switched off, while T<sub>2</sub> is switched on. Hence, the SUM current reaches 16µA, while C<sub>out</sub> remains 0.

Regarding ( $\Sigma$ in=3), the threshold detector switches T<sub>3</sub> and T<sub>9</sub> on, respecting to (2) the SUM output would be 0A, while C<sub>out</sub> would be 8 $\mu$ A.

If ( $\Sigma$ in=4), the threshold detector switches T<sub>3</sub> and T<sub>9</sub> on. Thus, SUM output equals to 8 $\mu$ A and C<sub>out</sub> remains 8 $\mu$ A.

While ( $\Sigma$ in=5), the transistors T<sub>3</sub> and T<sub>9</sub> switches on, in a same manner SUM output remains to 16 $\mu$ A and C<sub>out</sub> continues 8 $\mu$ A.

Finally if ( $\Sigma$ in=6), the threshold detector switches T<sub>3</sub> ,T <sub>4</sub>,T<sub>9</sub>,T<sub>10</sub> on, hence SUM equals to 0A due to (2), while C<sub>out</sub> would be 16µA because of the unification of two current flow paths.

Figure 3. The 1<sup>st</sup> proposed current-mode ternary full adder (CMTFA1) with the current mirror in SUM generator module last part

Figure 4. The 2<sup>nd</sup> proposed current-mode ternary full adder (CMTFA2) without the usage of current mirror in SUM generator module last part

# 4. RESULTS AND ANALYSIS

All of the proposed and previous designs (Figures 2, 3, 4) are simulated with Synopsys HSPICE and 32nm CNTFET technology [19, 20]. Simulations are done in 1V power supply with 1GHz operating frequency at room temperature.

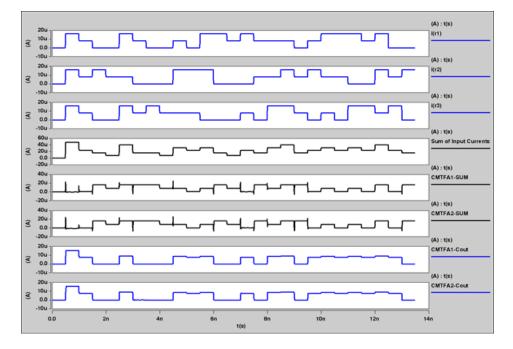

A random input pattern (Figure 5) is fed to the Full Adder cells to measure the delay parameter. However, the complete Ternary Full Adder cells can generate the expected outputs if that the sum of inputs reaches to 6 ( $0\le\Sigma$  in \le 6) (Figure 5).

The average power consumption is calculated during all of the transitions. The energy consumption (known as PDP), which makes a balance between delay and power, is calculated by the multiplication of delay time and power consumption [26, 27]. The average static power is also measured while the inputs are kept unchanged. All of the 27 possible different input patterns are fed to the circuits to measure the stand-by power dissipation. The average amount is reported as the static power. The simulation results are demonstrated in Table 2.

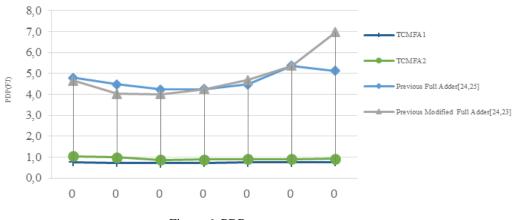

The proposed designs operate more efficiently than the previous ones. The simulation results show that the proposed Current-Mode Ternary Full Adders (CMTFA1 and CMTFA2) advantage from significant delay and power reductions, which is mainly due to the less transistor counts compared to the previous circuits. They also show greater reduction in terms of PDP, which originates from the elimination of a few transistors and shortening the critical path. Sensitivity to the variation of temperature is examined for the previous and proposed designs. The amount of energy consumption (PDP) versus a wide range of ambient temperatures, from 0°C to 70°C, is depicted in Figure 6. The proposed designs show insignificant sensitivity to temperature variations.

In addition, the capability of working in high frequencies such as 2GHz and 4GHz is examined for the previous and proposed designs. The results of energy consumption (PDP) versus frequency are depicted in Table 3.

| Table 2. The simulation results |              |                |          |              |             |

|---------------------------------|--------------|----------------|----------|--------------|-------------|

| Designs                         | Delay (psec) | Average        | PDP (fJ) | Static Power | No. of      |

| 8                               | 5 (1 )       | $Power(\mu W)$ | ~ /      | (µW)         | Transistors |

| Previous FA[24,25]              | 22.258       | 200.1          | 4.4537   | 186.87       | 33          |

| Previous Modified FA[24,23]     | 22.498       | 161.69         | 3.6377   | 148.41       | 30          |

| CMTFA1                          | 14.498       | 49.186         | 0.71312  | 28.882       | 14          |

| CMTFA2                          | 17.631       | 49.307         | 0.86935  | 28.894       | 14          |

|                                 |              |                |          |              |             |

# Table 2. The simulation results

| Table 3. The PDP variations versus frequency |              |            |          |  |

|----------------------------------------------|--------------|------------|----------|--|

| Block                                        |              | 1GHZ       |          |  |

|                                              | Delay (psec) | Power (µW) | PDP (fJ) |  |

| CMTFA1                                       | 14.498       | 49.186     | 0.71312  |  |

| CMTFA2                                       | 17.631       | 49.307     | 0.86935  |  |

| Previous FA[24,25]                           | 22.258       | 200.1      | 4.4537   |  |

| Previous Modified FA[24,23]                  | 22.498       | 161.69     | 3.6377   |  |

| Block                                        |              | 2GHZ       |          |  |

|                                              | Delay (psec) | Power (µW) | PDP (fJ) |  |

| CMTFA1                                       | 14.793       | 49.204     | 0.72786  |  |

| CMTFA2                                       | 17.972       | 49.349     | 8.8688   |  |

| Previous FA[24,25]                           | 22.246       | 200.35     | 4.4569   |  |

| Previous Modified FA[24,23]                  | 23.353       | 161.93     | 3.7816   |  |

| Block                                        |              | 4GHZ       |          |  |

|                                              | Delay (psec) | Power (µW) | PDP (fJ) |  |

| CMTFA1                                       | 14.87        | 49.248     | 0.73231  |  |

| CMTFA2                                       | 17.875       | 49.44      | 0.88388  |  |

| Previous FA[24,25]                           | 21.017       | 200.81     | 4.2204   |  |

| Previous Modified FA[24,23]                  | 22.504       | 162.45     | 3.6558   |  |

Figure 5. Input and output waveforms of proposed (CMTFA1,2)

#### TEMPRATURE(<sup>0</sup>C)

Figure 6. PDP versus temperature

One of the advantages of CML over VML is the elimination of speed degradation and performance loss when applying fan-out circuits. This mainly originates from the way that fan-out circuits are connected to a CML circuit [5]. To do this, the output currents are mirrored to the new branches, instead of a direct connection [5]. For this manner, simulations are redone twice more to investigate the mentioned capability: Firstly, with only one extra output load transistor. Secondly, four copies of the output current are also included in the analysis. Table 4 exhibits that the presence of the output load transistor and the connection of the fan-out circuits do not impact the cell delay time. These overheads do not increase extra load to the output nodes, whereas, voltage-mode circuits perform slower when the output load increases [5].

| Table 4. Delay parameter of the proposed designs versus the output load(s) |                     |                 |                                     |  |  |

|----------------------------------------------------------------------------|---------------------|-----------------|-------------------------------------|--|--|

| Designs                                                                    | With and anot I and | With The Output | With The Output Load Transistor and |  |  |

|                                                                            | Without any Load    | Load Transistor | 4 Copies of the Output Current      |  |  |

|                                                                            | Delay(ps)           | Delay(ps)       | Delay(ps)                           |  |  |

| CMTFA1                                                                     | 14.498              | 29.678          | 28.6790                             |  |  |

| CMTFA2                                                                     | 17.631              | 29.287          | 27.6020                             |  |  |

|                                                                            |                     |                 |                                     |  |  |

Two state-of-the-arts current-mode ternary full adders based on CNTFET technology (Mona Moradi)

# 5. CONCLUSION

New designs of Current Mode Ternary Full Adder cells based on CNTFET technology have been presented. The novel designs are based on mixed current and voltage logics. Adder cells respecting to their various applications could be designed in both CML and VML approaches, hence its performance can impact the performance of the system as a whole. The presented Ternary CML Full Adder cells based on CNTFET technology and MVCML specifications together, perform better than the previous cells. It can be utilized in mentioned applications in large CML circuits and units in future nano-electronics designs.

The novel designs of Full Adders lead to fewer transistors, TDs, and simple design. These specifications are due to higher performance of the proposed cells comparing the peer ones, which employ constant current sources as threshold detectors. It is worth to mention that conventional Ternary Full Adders must be able to perform with the complete sum of inputs ( $\Sigma$ in=6), whereas the previous designs are not capable of adding  $\Sigma$ in=6. Additionally, the load tolerance and capability of both proposed designs in large circuits have been studied. The simulation results indicate a great improvement in terms of power consumption, PDP, number of transistors, and driving capability. Regarding to simulation results, the best proposed CMTFA has approximately 80% higher efficiency than the best previous design in terms of PDP.

### ACKNOWLEDGEMENTS

This paper has been supported by Young Researcher and Elite Club, Roudehen Branch, Islamic Azad University, Roudehen, Iran.

#### REFERENCES

- Dubrova, E., "Multiple-valued logic in VLSI: Challenges and opportunities," *In Proceedings of NORCHIP*, vol. 99, pp. 340-350, 1999.

- [2] Navi, K., Kazeminejad, A. and Etiemble, D., "Performance of CMOS current mode Full Adders," *Proceedings of 24th International Symposium on Multiple-Valued Logic (ISMVL'94)*, pp. 27-34, 1994.

- [3] Kameyama, M., Kawahito, S. and Higuchi, T., "A multiplier chip with multiple-valued bidirectional current-mode logic circuits," *Computer*, vol. 21, no. 4, pp. 43-56, 1988.

- [4] Temel, T. and Morgul, A., "Multi-valued logic function implementation with novel current-mode logic gates," In IEEE International Symposium on Circuits and Systems, 2002 (ISCAS 2002), pp. 1, pp. 881-884, 2002.

- [5] Moradi, M., Faghih Mirzaee, R., and Navi, K., "New Current-Mode Integrated Ternary Min/Max Circuits without Constant Independent Current Sources," *Journal of Electrical and Computer Engineering*, pp. 1-11, 2015.

- [6] Moradi, M., Mirzaee, R.F. And Keivan, Navi, "New Current-Mode Multipliers by CNTFET-Based n-Valued Binary Converters," *IEICE Transactions on Electronics*, vol. 99, no. 1, pp. 100-107, 2016.

- [7] Delİcan, Y. and Yildirim, T., "High performance 8-bit mux based multiplier design using MOS current mode logic," *In 2011 7th International Conference on Electrical and Electronics Engineering (ELECO)*, pp. II-89, 2011.

- [8] Smith, K.C., "A multiple valued logic: a tutorial and appreciation," *Computer*, vol. 4, pp. 17-27, 1988.

- [9] Liang, B., Ma, K., Ding, Z. and Fu, X., "The structure design of MOS current mode logic adder," In 2012 International Conference on Microwave and Millimeter Wave Technology (ICMMT), vol. 4, pp. 1-4, 2012.

- [10] Ebrahimi, S., Keshavarzian, P., Shahsavari, M., Sorouri, S., "Low Power CNTFET-Based Ternary Full Adder Cell for Nanoelectronics," *International Journal of Soft Computing and Engineering (IJSCE)*, vol. 2, pp. 291-295, 2012.

- [11] Lin, S., Kim, Y.B. and Lombardi, F., "CNTFET-based design of ternary logic gates and arithmetic circuits," *IEEE Transactions on Nanotechnology*, vol. 10, no. 2, pp. 217-225, 2011.

- [12] Jamalizadeh, M., Sharifi, F., Moaiyeri, M.H., Navi, K. and Hashemipour, O., "Five new MVL current mode differential absolute value circuits based on carbon nano-tube field effect transistors (CNTFETs)," *Nano-Micro Letters*, vol. 2, no. 4, pp. 227-234, 2010.

- [13] Temel, T. and Morgul, A., "Implementation of multi-valued logic gates using full current-mode CMOS circuits," *Analog Integrated Circuits and Signal Processing*, vol. 39, no. 2, pp. 191-204, 2004.

- [14] Navi, K., Kazemi P., and Ghorbannia, D., "Very High Speed Current Mode Logical Circuits," *The CSI Journal of Computer Science and Engineering*, pp. 45-50, 2005.

- [15] Avouris, P., Appenzeller, J., Martel, R. and Wind, S.J., "Carbon nanotube electronics," *Proceedings of the IEEE* vol. 91, no. 11, pp. 1772-1784, 2003.

- [16] Radhakrishnan, D., "Low-voltage low-power CMOS full adder," In IEE Proceedings Circuits, Devices and Systems, IET, vol. 148, no. 1, pp. 19-24, 2001.

- [17] Lin, J.F., Hwang, Y.T., Sheu, M.H. and Ho, C.C., "A novel high-speed and energy efficient 10-transistor full adder design," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 54, no. 5, pp. 1050-1059, 2007.

- [18] Lin, S., Kim, Y.B., Lombardi, F. and Lee, Y.J., "A new SRAM cell design using CNTFETs," *IEEE 2008 International SoC Design Conference*, vol. 1, pp. I-168, 2008.

- [19] Deng, J. and Wong, H.P., "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region," *IEEE Transactions on Electron Devices*, vol. 54, no. 12, pp. 3186-3194, 2007a.

Int J Reconfigurable & Embedded Syst, Vol. 9, No. 1, March 2020: 19-27

- [20] Deng, J. and Wong, H.P., "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part II: Full device model and circuit performance benchmarking," *IEEE Transactions on Electron Devices*, vol. 54, no. 12, pp. 3195-3205, 2007b.

[21] "Stanford University CNFET Model," Stanford Nanoelectronics Lab, 2007. [Online]. Available:

- [21] "Stanford University CNFET Model," Stanford Nanoelectronics Lab, 2007. [Online]. Available: http://nano.stanford.edu/model.php?id=2.

- [22] Navi K., Doostaregan A., Moaiyeri M.H., Hashemipour O., "A hardware-friendly arithmetic method and efficient implementations for designing digital fuzzy adders," *Fuzzy Sets and Systems*, vol. 185, no. 1, pp. 111-124, 2011.

- [23] Shen, J. and Chen, X., "Design of symmetric ternary current-mode CMOS circuits," *Journal of Electronics* (China), vol. 14, no. 4, pp. 336-344, 1997.

- [24] Xunwei, W., Xiaowei, D. and Shiyan, Y., "Design of ternary current-mode CMOS circuits based on switch-signal theory," *Journal of Electronics* (China), vol. 10, no. 3, pp. 193-202, 1993.

- [25] Zhou, Q.N., Yu, M.Y. and Ye, Y.Z., "On-chip voltage down converter with precision CMOS current source for VLSI chip," In 2005 IEEE Conference on Electron Devices and Solid-State Circuits, pp. 375-378, 2005.

- [26] Moradi, M., Mirzaee, R.F., Moaiyeri, M.H. and Navi, K., "An applicable high-efficient CNTFET-based full adder cell for practical environments," *In 2012 16th CSI International Symposium on Computer Architecture and Digital Systems (CADS)*, pp. 7-12, 2012.

- [27] Moaiyeri, M.H., Mirzaee, R.F., Doostaregan, A., Navi, K. and Hashemipour, O., "A universal method for designing low-power carbon nanotube FET-based multiple-valued logic circuits," *Computers & Digital Techniques, IET*, vol. 7, no. 4, pp. 167-181, 2013.

# **BIOGRAPHIES OF AUTHORS**

Mona Moradi received her B.S. and M.Sc. degrees in Hardware Engineering. She has Ph.D. degree in 2015 at Science and Research Branch of Islamic Azad University under supervision of Prof. Keivan Navi. Her research interests include VLSI, Digital Integrated Circuits, MVL, Arithmetic Circuits, CNTFET, nano electronic, hardware security and Cryptography. She is now assistant professor at Islamic Azad University in Roudehen branch.