# Switching pulse generation for DC-DC boost converter using xilinx-ISE with FPGA processor

## R. Palanisamy, K. Vijayakumar

Department of EEE, SRM Institute of Science and Technology, Kattankulathur, Chennai, India

## ABSTRACT

## Article Info Article history:

ReceivedJan 20, 2019 Revised Apr 1, 2019 Accepted Apr 25,2019

#### Keywords:

DC-DC boost converter Field Programmable Gate Array (FPGA) Processor Hardware Description Language (VHDL) Xilinx-ISE This paper explains steps to generate switching pulse using Xilinx-ISE with FPGA processor for DC-DC boost converter. The switching pulse generated using Very high speed integrated circuit Hardware Description Language (VHDL) with Xilinx-ISE. VHDL is a programming language, which is used to model and design any complex circuits in a dynamic environment. This paper gives the course of action for generation of switching pulses for DC-DC boost converter using Xilinx-ISE and matlabsimulink. The switching pulse generated using Xilinx-ISE with FPGA-Spartan 6 processor compared with switching pulse generated using matlab.

Copyright © 2019 Institute of Advanced Engineering and Science. All rights reserved.

#### Corresponding Author:

HariSoetanto, Department of EEE, SRM Institute of Science and Technology, Kattankulathur, Chennai, India. Email: palanisamy.r@ktr.srmuniv.ac.in

#### 1. INTRODUCTION

In recent years the usage and progress of Programmable Logic Devices (FPGA, CPLD) are increasing for the power electronic applications without microprocessors (CPU or DSP) and microcontrollers. Complex control algorithm can be implementing for any power electronic system using FPGA processor and computational time also significantly reduced using programmable logic devices. But in terms of business based applications for power electronic systems are designed using microprocessor and microcontroller [1].

Generally to improve the output of renewable energy system or dc source, the DC-DC boost converters are employed. The relevance of DC-DC converters engross the following requirements like high step up output voltage gain, low input current and low current ripples, high output voltage and low voltage ripples and higher efficiency. The various DC-DC converters are design with help of conventional coupled inductor, switched capacitor, clamping diodes and controlled power semiconductor device, which is controlled by duty ratio. Based on duty ratio of DC-DC converter the output voltage can be increased or decreased. In this paper gives the procedure to generate switching pulse for DC-DC boost converter using Xilinx-ISE with FPGA processor and matlab. The hardware results for DC-DC boost converter are obtained using Spartan-6 FPGA processor [2-6]

## 2. DC-DC BOOST CONVERTER

The DC-DC converter is electronic system which converts dc source voltage from one voltage range to another voltage range. It attracts many researchers to boost or increases output voltage from the renewable energy systems like fuel cell, PV system and wind energy system. The conventional

DC–DC converters are power switching converter which innately introduces a certain amount ripple in current output, which is minimized with help of advanced DC-DC converters [4].

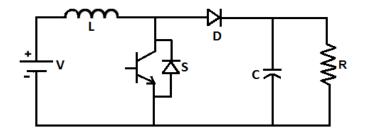

Generally the conventional DC-DC converters only applicable for low power applications, which are developed to high power applications using isolated and non isolated converters. In Figure 1 shows the diagram for boost converter, which is used to boost input dc voltage. When the power switch is ON condition, the inductor charge energy in the form of electromagnetic field and discharge energy when power switch is off condition. The time constant RC of the circuit depends on the capacitor size. The output voltage boost level depends on the duty ratio of the switch and applied input voltage, which is defined as,

$$V_0 = V_i \, (1 - G) \tag{1}$$

Where, Vo is output voltage, Vi-input voltage and G-duty ratio.

Figure 1. Circuit diagram of DC-DC Boost converter

#### 3. SWITCHING PULSE GENERATION

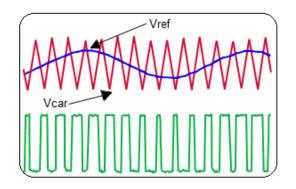

The switching pulse for DC-DC boost converter is generated using Sinusoidal Pulse Width Modulation (SPWM). Pulse Width Modulation is a method wherein a fixed DC input voltage is given to inverters and controlled AC output voltage is obtained by adjusting the duty cycle. Output signal alternates between ON and OFF within specified period; controls power received by a device and the voltage seen by the load is directly proportional to the source voltage. Pulse Width Modulation allows us to vary how much time the signal is high in an analog way. While the signal can only be high (usually 5V) or low (ground) but we can vary the proportion of time the signal is high compared to when it is low is shown in Figure 2 [7-9].

Figure 2. SPWM-switching pulse generation

The main advantage of PWM is that power loss in the switching devices is very low. The technique we are using is the Sinusoidal Pulse Width Modulation. SPWM is one of the most popular modulation technique used and finds more applications in industries. The gating signal can be generated by comparing a sinusoidal reference signal with a triangular carrier wave and width of each pulse varied proportionally to amplitude of a sine wave evaluated at the centre of same pulse. SPWM is one technique which helps in reducing the harmonics present in quasi state [10-13].

| Int J Reconfigurable & Embedded Syst | ISSN: 2089-4864 | <b>□</b> 83 |

|--------------------------------------|-----------------|-------------|

| The modulation index is defined as,  | Ma=Am/Ac        | (2)         |

Where,  $A_m$  = reference signal amplitude, Ac=carrier signal amplitude.

## 4. VHDL CODING USING XILINX-ISE

The switching pulse for dc/dc converter is engendered using VHDL coding by Xilinx ISE with help of FPGA processor. Xilinx-ISE is the platform environment for writing VHDL code and to feed into the FPGA processor. To generate single switching pulse for dc/dc converter the following VHDL coding written in Xilinx software.

## 4.1. Coding

```

Library IEEE

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD LOGIC ARITH.ALL;

Entity top_SPWM

Port (CLK: IN STD_LOGIC;

PWM DIR: OUT STD LOGIC;

PWM OE: OUT_STD_LOGIC;

PWM 1: OUT STD_LOGIC; );

ARCHITECTURE BEHAV OF TOP PWM IS

Signal CAR: integer:=0

Begin

Process(clk)

Variable counter: integer:=0;

Begin

ifrising_edge(clk) then

COUNTER:=COUNTER+1;

If counter > 0 and counter <=1000;

CAR \le CAR + 1;

ELSEIF COUNTER >1000 AND COUNTER <= 2000 THEN

CAR<=CAR-1;

ELSEIF COUNTER >2000 THEN

COUNTER:=0;

CAR<=0:

END IF:

END IF:

IF 500>=CAR THEN

PWM 1<= '1';

ELSE

PWM 1 <= '0';

END IF;

END PROCESS:

```

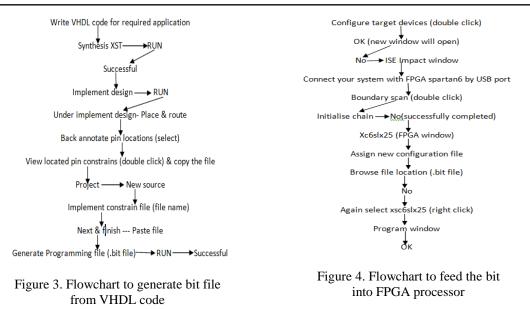

## 4.2. Steps to generate bit file from VHDL coding

After initializing the spartan-6 FPGA processor; the VHDL has written for single switching pulse generation to control the DC-DC converter. The flowchart for generation of bit files from VHDL code is shown in Figure 3. And the generated bit file is feed into the FPGA processor to control the DC-DC converter, which is shown in Figure 4.

Next calculated the difference in the value of the parameter value of the patient and the value of the ideal parameter value for a particular drug. For example, the difference between the value of the parameter in with the value of the ideal parameter of the diuretic drug type is shown in.

#### 5. SIMULATION AND HARDWARE RESULTS AND DISCUSSION

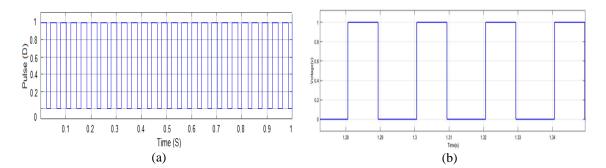

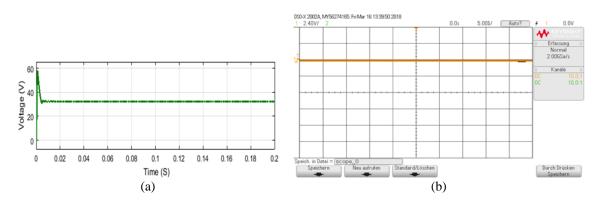

The system is simulated and implemented to generate switching pulse using Xilinx-ISE with FPGA processor for DC-DC boost converter. The switching pulse generated using Very high speed integrated circuit Hardware Description Language (VHDL) with Xilinx-ISE. VHDL is a programming language, which is used to model and design any complex circuits in a dynamic environment. The switching pulse generated through SPWM method and it is implemented through FPGA professor with help of Xilinx software, which is shown in Figure 5. The DC input supply applied to DC-DC converter is 12V and it is converted 32V, which is 2.6 times of applied input voltage and is shown in Figure 6.

Figure 5. Switching pulse generation using SPWM (a) simulation (b) hardware

Figure 6. Output voltage of dc-dc boost converter (a) simulation (b) hardware

#### 6. CONCLUSION

Generally various DC-DC converter topologies are used for energy conversion system. In this paper, switching pulse generation for dc to dc converter using Xilinx–Spartan 6 controller. The output voltage of the DC-DC converters are varied, which attains as increased, decreased or equal to applied voltage depends on the duty ratio produced by the sinusoidal pulse width modulation technique. The simulation & hardware results are verified using matlab/simulink and FPGA processor

#### REFERENCES

- [1]. Yang, W. Li, Y. Zhao, and X. He, "Design and analysis of a grid connected PV power system,"*IEEE Trans.Power Electron.*, vol. 25, no. 4, pp. 992–1000, Apr. 2010.

- [2]. J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital PI controller," *IEEE Trans. Ind. Electron.*, vol. 56, no. 1, pp. 149–158, Jan. 2009.

- [3]. L. S. Yang, T. J. Liang, H. C. Lee, and J. F. Chen, "Novel high step-up DC-DC converter with coupledinductor and voltage doubler circuits," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 4196–4206, Sep. 2011.

- [4]. Q. Zhao and F. C. Lee, "High-efficiency, high step-up DC–DC converters,"*IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 65–73, Jan. 2003.

- [5]. R. Palanisamy, K. Vijayakumar "Maximum Boost Control for 7-level z-source cascaded h-bridge inverter ", International Journal of Power Electronics and Drive Systems, vol 8, Issue 2, June 2017.

- [6]. W. Yu, H. Qian, and J. S. Lai, "Design of high-efficiency bidirectional dc-dc converter and high-precision efficiency measurement," IEEE Trans Power Electron., vol. 25, no. 3, pp. 650-658, Mar. 2010.

- [7]. Y. R. J. Wai and R. Y. Duan, "High step-up converter with coupled inductor," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1025–1035, Sep. 2005.

- [8]. R. Palanisamy, K. Vijayakumar, Komari Nikhil, MadhumathiIyer, RamachandarRao, "A Proposed SVM for 3level Transformer-less Dual Inverter Scheme for Grid Connected PV System" *Indian Journal of Science and Technology*, 2016 Nov, 9(42).

- [9]. Poh Chiang Loh, FengGao, FredeBlaabjerg, and Sokweilim. Operational Analysis and Modulation Control of ThreeLevel Z-Source Inverters With Enhanced Output Waveform Quality. *IEEE Transaction on Power Electronics*, July 2010. Vol.24, No.7.

- [10]. S.C.Tan, Y.M.Lai, C.K. Tse, "Implementation of Pulse-Width- Modulation based Sliding Mode Controller for Boost converters," IEEE Power Electronics Letters, vol.3, No.4, Dec. 2006, pp.130-135.

- [11]. S.S.Muley, R.M.Nagarale, "Sliding Mode Control Of Boost converter," *IJETAE* ISSN:2250-2259, vol.3, Issue 9, Sept.2013.

- [12]. R. Palanisamy, A.U Mutawakkil, K. Vijayakumar "Hysteresis SVM for coupled inductor z source diode clamped 3-level inverter based grid connected PV system", International Journal of Power Electronics and Drive Systems, vol 7, Issue 4, Dec 2016.

- [13]. Q. Zhao and F. C. Lee, "High-efficiency, high step-up DC–DC converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 65–73, Jan. 2003.