# An Ultra Low Power CMOS Sigma Delta ADC Modulator for System-on-chip (SoC) Temperature Sensor for Aerospace Applications

# Deepak Prasad' Vijay Nath

Departement of Electronics and Communication Engineering, Birla Institute of Technology, Mesra, Ranchi, India

# **Article Info**

#### Article history:

Received Dec 5, 2017 Revised Jan 20, 2018 Accepted Feb 7, 2018

#### Keywords:

Clocked comparator CMOS DAC Integrator Op-amp Signal to Noise Ratio (SNR)

# ABSTRACT

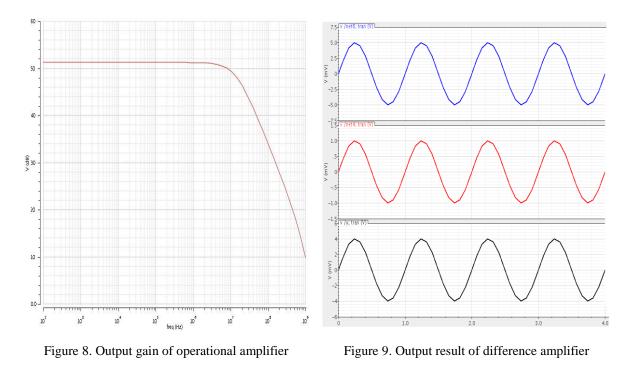

In the current paper, an accurate with low power consumed sigma delta ( $\Sigma\Delta$ ) analog to digital converter has been designed for the aerospace applications. The sigma delta ADC has been designed in such a way that it works fine with consumption of low power and high accuracy in the system on chip (SoC) temperature sensor where the analog output from the temperature sensor unit will be the fed to the analog to digital converter. To check the robustness, different parameters with variation has been analyzed. The high gain operational amplifier plays a vital role in the circuits design. Hence, a 30 MHz operational amplifier has also been proposed whose unity gain bandwidth (UGB) has been observed of about 30 MHz, 51.1dB dc gain and slew rate (SR) of about 27.9 V/  $\mu sec.$  For the proper operation of the circuit, a power supply of +1.3V to -1.3V is used. The proposed sigma delta ADC modulator is showing better results over previously designed modulator in terms of power consumption, error and performance. The design and simulation have been tested with the help of cadence analog design environment with UMC 90nm CMOS process technology.

> Copyright © 2018 Institute of Advanced Engineering and Science. All rights reserved.

# Corresponding Author:

Deepak Prasad, Departement of Electronics and Communication Engineering, Birla Institute of Technology, Mesra, Ranchi-835215, Jharkhand, India. Email: prasaddeepak007@gmail.com

# 1. INTRODUCTION

The continuous innovation of technology has demanded an entire circuit system to be embedded on a single chip. System-on-chip temperature sensor requires a high performance, least inaccurate, more efficient, reliable and robust analog to digital converter which can be used to convert the analog signal receiving from the temperature sensor into digital domain. The data in digital domain is much safer, can be transferred, copied easily compared to analog domain. In terms of accuracy and high signal to noise ratio (SNR), sigma delta ( $\Sigma\Delta$ ) ADC is the best choice in compared to available ADC as they cannot gain very high accuracy. The sigma delta ( $\Sigma\Delta$ ) ADC comprises of two part i.e. sigma delta modulator and digital filter. The modulator part combines sampling at the rate equal and above to Nyquist rate with negative feedback while the preceding digital filter exchanges the amplitude for the resolution in time. Furthermore, sigma delta ( $\Sigma\Delta$ ) ADC has a capability to tolerate the imperfection of analog circuit up to great extend. Sigma delta ( $\Sigma\Delta$ ) provides the implementation of high density and complex analog circuit.

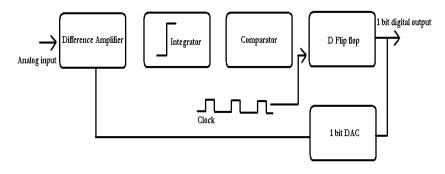

Therefore it becomes the first priority to realize in system-on-chip (SoC). The block diagram of sigma delta modulator is sjowun in Figure 1. The designed sigma delta ( $\Sigma\Delta$ ) ADC modulator consists of an integrator. The forward path of high order sigma delta ( $\Sigma\Delta$ ) ADC modulator contains more than one integrator which no doubt offers great resolution but unfortunately it suffers from potential instability [1], [2]. However, single order sigma delta ( $\Sigma\Delta$ ) ADC modulator may be cascaded to get precise gain. The order of

sigma delta ( $\Sigma\Delta$ ) ADC modulator varies with its applications. The input signal to sigma delta ( $\Sigma\Delta$ ) ADC modulator is sampled at high frequency and thus the conversion of analog signal into digital pulse takes place. The bad filtering process result into generation of digital pulse engulfed of unwanted noise [3], [4].

Figure 1. Block diagram of sigma delta modulator

The resolution of obtained output is directly dependent on the order of modulator and the sampling ratio which is decided at the modulator stage. Earlier the anti-aliasing filter was being considered but the principle of oversampling ratio ends the requirement of it, since now the analog input signal can be sampled directly using oversampling clock [6], [7]. Hence, an improved and accurate ultra low power sigma delta ( $\Sigma\Delta$ ) ADC modulator has been designed and argued in this paper. The rest of the article is patterned as follows. Section II enlightens the proposed circuit's configuration with the detailed depiction of each unit. Section III is dedicated to the results and discussion. Finally, section IV wraps up the work and the article ends with conclusions and acknowledges to the funding agency Indian Space Research Organization (ISRO) (India). The sigma delta ( $\Sigma\Delta$ ) ADC modulator shown in Figure.1 consists of a difference amplifier, an integrator, a comparator, a D flip flop and a DAC in the feedback loop of the modulator. The input analog signal has been passed through several processes like oversampling, quatization and noise shaping before it comes into pulse train at output. Both the conversion processess i.e. analog to digital (ADC) and digital to analog (DAC) conserves a vital space in modern technology [8], [9].

# 2. PROPOSED CIRCUIT CONFIGURATION

# 2.1. Operational Amplifier

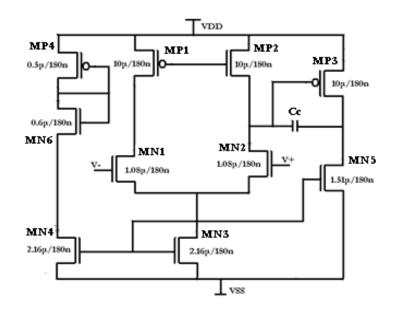

The wide applications of operational amplifier make it a key ingredient to many analog systems. Basically it consists of a differential amplifier which amplifies the difference between two input signals. The differential amplifier also provides a required gain. To further improvise the gain of an operational amplifier, a second stage of common source stage is attached. Miller compensation technique has been implemented here for the stability of system. On the other hand, coupling capacitor found it place inbetween the common source amplifier's input and final stage of differential amplifier. Figure 2 shows the schematic of proposed operational amplifier. Mostly the feedback in operational amplifier is imposed to make the transfer function of system independednt of gain. But in high frequency applications, as the frequency increases, gain slightly decreases and making transfer function unstable. To avoid this unstability, op-amps must be chosen of broad band for high frequency applications. The sizes of different transistors used in Fiigure 2 are tabulated in Table 1.

The two stage architecture has the disadvantage of having two impedance nodes which are indicated by A and B due to which two pole will be dominant which will deteriorate the phase margin of the op amp. Hence, a Miller capacitance ( $C_c$ ) has been introduced between A and B to resolve it. The chosen value must satisfy the following equation [10].

$$C_{c} = (\frac{2.2}{10})C_{L} \tag{1}$$

Where, coupling capacitor is denoted by  $C_c$  while load capacitorn is expressed as  $C_L$ . Similarly, the unity gain bandwidth product (GB) is termed as,

$$B = \frac{g_{m1}}{C_c} \tag{2}$$

Where,  $g_{m1}$  is the input transconductance. For the gain-bandwidth product to be high the input transconductance should be high, by making the channels of MN1 and MN2 wide. Similarly the output capacitance should be low.

Figure 2. Proposed schematic of Op-amp

Variation in W and L can be made by using following Equation (3).

$$g_m = \sqrt{2\mu_p C_{ox} W/_L I_d} \tag{3}$$

Slew rate decides the current flowing in the transistor MN5, and is determined by how fast can be charged and discharged. This is given by Equation (4)

$$Slew Rate = \frac{I_s}{C_c}$$

(4)

The aspect ratio of transistor MP3 is decided by the positive input common mode range. Output pole should be assumed at the location which is approx 2.2 times for phase margin of 60°. Hence,  $g_{m6}$  is determined by the following Equation (5)

$$g_{m6} = 2.2g_{m2} \left( \frac{C_L}{C_C} \right) \tag{5}$$

| Table 1. Sizes of Transistor Utiliz | zed in C | ircuit 2 |

|-------------------------------------|----------|----------|

|-------------------------------------|----------|----------|

| Transistor | Width (W) | Length (L) | Used in |  |  |  |  |

|------------|-----------|------------|---------|--|--|--|--|

| MP1        | 10µm      | 0.18 µm    | Fig.2   |  |  |  |  |

| MP2        | 10µm      | 0.18 µm    | Fig.2   |  |  |  |  |

| MP3        | 10µm      | 0.18 µm    | Fig.2   |  |  |  |  |

| MP4        | 0.5µm     | 0.18 µm    | Fig.2   |  |  |  |  |

| MN1        | 1.08 µm   | 0.18 µm    | Fig.2   |  |  |  |  |

| MN2        | 1.08 µm   | 0.18 µm    | Fig.2   |  |  |  |  |

| MN3        | 2.16 µm   | 0.18 µm    | Fig.2   |  |  |  |  |

| MN4        | 2.16 µm   | 0.18 µm    | Fig.2   |  |  |  |  |

| MN5        | 1.51 µm   | 0.18 µm    | Fig.2   |  |  |  |  |

| MN6        | 0.6 µm    | 0.18 µm    | Fig.2   |  |  |  |  |

# 2.2. Difference apmlifier and integrator

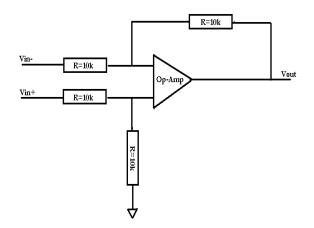

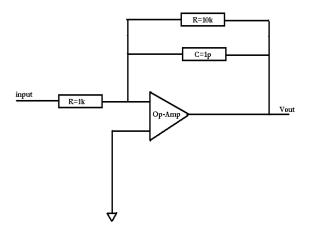

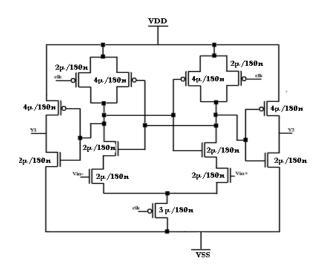

Difference amplifier comes under the list of applications of operational amplifier. The design of difference amplifier uses two stage operational amplifier. Since it shows good voltage gain, CMRR, slew rate, it is adopted here. The difference amplifier is basically having two input terminals i.e.  $V_2$  and  $V_1$  and one output terminal ( $V_{out}$ ). The output is the difference of the two inputs. On the other hand, The CMOS integrator performs mathematical operation on input and produces an output which is proportion to the integral of the input voltage. Figures 3 and 4 show the schematic of difference amplifier and integrator. Integrator is the important building block used in the design of continuous time filters [11]. The change in the combination of resistance and capacitor values changes the value of RC time constant which further affects the rate of change of output voltage.

Figure 3. Schematic of difference amplifier

Figure 4. Schematic of integrator

Ideally the summation of previous output v(kT - T) and previous input u(kT - T) gives the output of the integrator.

$$v(kT) = g_0 u(kT - T) + v(kT - T)$$

(6)

The constant  $g_0$  represents the gain preceding the input to integrator. Equation (6) is corresponding to the transfer function of an ideal integrator shown in Equation (7).

$$H(z) = \frac{g_0 z^{-1}}{1 - z^{-1}} \tag{7}$$

# 2.3. Comparator

In compare to other units of sigma delta ( $\Sigma\Delta$ ) ADC modulator, comparator is the most fundamental component as the comparison of two different analog inputs signal and make out of single digital output signal have been done in this unit. It has a vital impact on the performance and reliability of the designed circuit. The schematioc of proposed comparator is shown in Figure 5. The input offset voltage, delay and the range of the input signal decides the speed and resolution of analog to digital converter [12]. The basic property of the comparator is to take the analog input and gives a binary or digital output. Clocked comparators are often called dynamic comparator. Regenerative feedback is often used in dynamic comparator and occasionally in non clocked comparator. Dynamic comparator is used in the design of high speed ADCs.

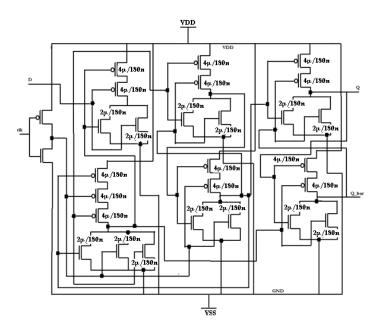

# 2.4. D flip flop

The used D flip flop has three interconnected RS latch circuits. In designing, any of NAND or NOR can be used. When clock gets logic 1, the output latch gets isolated from any input changes as the output of the two middle input gates is forced to get logic 0. On the other hand, the input latych with an illegal state will automatic resume its latching action, when logic 0 is triggered by clock. Figure 6 depicts the schematic of proposed D flip-flop.

Figure 5. Proposed schematic of comparator

Figure 6. Proposed schematic of D flip-flop

**D** 17

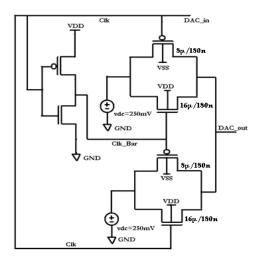

# 2.5. 1 bit DAC

Basically digital signal or code is converted into analog voltage or current by using digital to analog converter (DAC). The DAC is comprised of reference voltage ( $V_{ref}$ ), supply voltage ( $V_{dd}$ ) and analog output. True analog quantity has not been observed at the output of the digital to analog converter (DAC). The schematic of proposed 1 bit DAC is shown in Figure 7. The output is found in pseudo analog quantity. The number of input bits should be increased, since the obtained analog output is proportional to its digitalpulse input. Therefore the step size gets reduced and due to higher number of bits, the output seems to b analog signal.

Figure 7. Proposed schematic of 1 bit DAC

# 3. RESULTS AND ANALYSIS

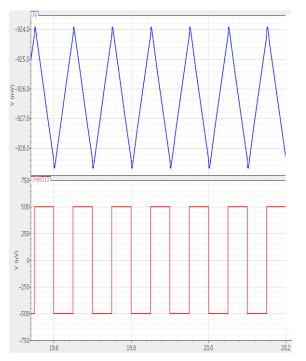

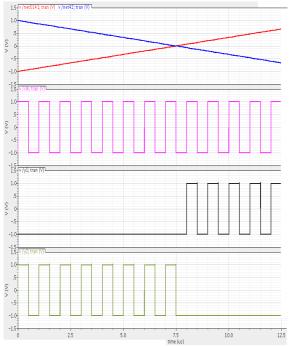

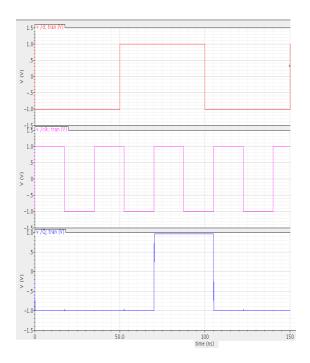

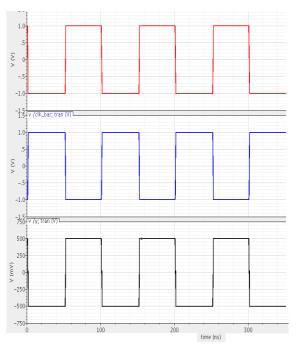

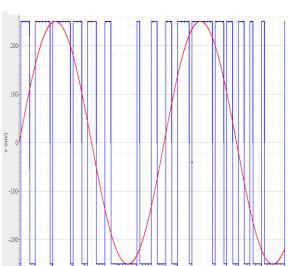

The components and the final designed sigma delta modulator are simulated using UMC 90nm. The output gain of operational amplifier is depicted in Figure 8. While the simulated results of difference amplifier as shown in Figure 9, integrator as shown in Figure 10, Comparator as shown in Figure 11, D flip-flop as shown in Figure 12, 1bit DAC as shown in Figure 13 and sigma delta modulator as shown in Figure 14. Comparison of work done in this paper has been compared in Table 2.

An Ultra Low Power CMOS Sigma Delta ADC Modulator for System-on-chip (SoC) ... (Deepak Prasado)

Figure 10. Output result of integrator

Figure 11. Output result of clocked comparator

Figure 12. Output result of D flip flop

Figure 13. Output result of 1 bit DAC

Figure 14. Output result of Sigma Delta ( $\Sigma\Delta$ )

1.0 time (ius)

Table 2. Comparison with Some Other Recent Work

| Factor        | [5]       | [13]  | [14]   | [16]   | [17]   | [18]   | [15]    | [19]   | This  |

|---------------|-----------|-------|--------|--------|--------|--------|---------|--------|-------|

|               |           |       |        |        |        |        |         |        | Work  |

| Process       | 0.18µm    | 130nm | 180nm  | MATLAB | 0.18µm | 0.35mm | 0.35 µm | 0.13nm | 90nm  |

| Technology    | CMOS      | CMOS  | CMOS   |        | CMOS   | CMOS   | CMOS    | CMOS   | CMOS  |

| Architecture  | Flash     | Sigma | Sigma  | Sigma  | Sigma  | Sigma  | Flash   | Flash  | Sigma |

|               |           | Delta | Delta  | Delta  | Delta  | Delta  |         |        | Delta |

| Input Voltage | 0 to 1.8V | 1V    | 2V     |        | 1V     | 3.3V   | 3V      | 1.5V   | 1.3V  |

| SNR           |           | 78dB  |        | 82dB   | 85.2dB | 85dB   | 73 dB   |        | 62dB  |

| Power         | 36.23mW   | 68µW  | 6.45µW |        | 1.96mW | 200mW  | 341mW   | 160mW  | 54µW  |

| dissipated    |           |       |        |        |        |        |         |        |       |

### 4. CONCLUSION

In the present paper, an ultra low power sigma delta ( $\Sigma\Delta$ ) ADC modulator which is highly useful in system on chip (SOC) temperature sensor for aerospace applications has been described. Comparison of work done in this paper has been compared in Table 2. The each unit of sigma delta delta ( $\Sigma\Delta$ ) ADC modulator is examined and modeled here. The proposed sigma delta delta ( $\Sigma\Delta$ ) ADC modulator works utilizing minimal power supply of +1.3V to -1.3V. The average power of 54  $\mu$ W is dissipated with the smapling frequency of 50MHz.

### **ACKNOWLEDGEMENTS**

We are thankful to RESPOND ISRO, Bangalore for funding this research work. The sanction number is ISRO/RES/3/679/15-16. We also thankful to Prof. S. Pal, HOD ECE, Prof. S. Konar, Dean (SR & FA) and Prof. M.K. Mishra, Vice-chancellor, BIT Mesra Ranchi for providing infrastructure facility to carry out this research work.

#### REFERENCES

- J. C. Candy, "Decimation for sigma delta modulation," IEEE Trans. Commun., vol. COM-34, pp. 72- 76, Jan. 1986.

- [2] S. Ardalan and J. Paulos, "An analysis of nonlinear behavior in delta-sigma modulators," IEEE Trans. Circuits Syst., vol. CAS-3, pp. 593-603, June 1987.

- [3] S. R. Norsworthy, R. Schreier and G. C.Temes, "Delta Sigma data converters: Theory, Design and Simulation," New York, IEEE press, 1996.

- [4] N. Mukahar and S. H. Ruslan, "A 93.36 dB, 161 MHz CMOS Operational Transconductance Amplifier (OTA) for a 16 Bit Pipeline Analog to Digital Converter (ADC)," International Journal of Electrical and Computer Engineering (IJECE), vol. 2, pp. 106-111, Feb 2012.

- [5] M. Marufuzzaman, S Z. Abidin, M. B. I. Reaz, L. F. Rahman, "Design of 3 bit ADC in 0.18µm CMOS Process", Telkomnika Indonesian Journal of Electrical Engineering, vol. 12, pp. 5197-5203, July 2014.

- [6] Y. Fan, Y. Huijing, L. Gang, "A High Performance Sigma- Delta ADC for Audio Decoder Chip," Telkomnika, vol. 11. Pp. 6570-6576, Nov. 2013.

- [7] S. H. Ardalan and J. J. Paulos, "An analysis of non linear behaviour in delta sigma modulator," IEEE Trans. circuits and sys. Vol. 34, pp-593-603, June 1987.

- [8] R. Thankachan, K. R Jayakrishnan and T. K Shahana, "Design of 1 bit DAC for delta sigma modulator," in International Conference on Emerging Trends in Technology and Applied Sciences, 2015, pp-19-22.

- [9] B. Razavi, "Design of CMOS Analog Integrated Circuits", McGraw Hill, California, 1998.

- [10] P.E.Allen and D.R.Holberg, "CMOS circuit design," Oxford Indian Edition, 2009.

- [11] V. D. Kamath, "Overview of OP-AMP and OTA based integrators" International Journal of innovative research in electrical, electronics, instrumentation and control engineering, Vol-3, pp-74-81, September 2015.

- [12] S. R. Norsworthy, R. Schreier & G. C. Temes, "Delta Sigma Data Converters: Theory, Design and Simulation," New York, IEEE press,1998

- [13] K. L. Krishna, T. Ramashri, D. Reena, "A 1V second order delta sigma ADC in 130nm CMOS," in International Conference on Information Communications and Embedded Systems, Feb.2014.

- [14] H. Dosi, R. Agrawal," Low power 8 bit analog to digital converter in 180nm CMOS technology,"International Journal of Science and Research (IJSR) Vol-2, pp. 417-418, July 2013.

- [15] W. Yang, D. Kelly, I. Mehr, M. T. Sayuk and L. Singer, "A 3V 340mW 14b 75 Msample/s CMOS ADC with 85dB SFDR at Nyquist Input", IEEE Journal of Solid State Circuits, vol. 36., pp. 1931-1936, Dec. 2001.

- [16] Y. Shaojun, T. Ziquan, J. Yueming and D. Naiying, "The design of multi bit sigma delta ADC modulator," in 2<sup>nd</sup> International Conference on measurement information and control, China, 2013.

- [17] M. A. Sohel, K. C. K. Reddy, S. A. Sattar "Design of low power sigma delta ADC" International Journal of VLSI design and communication systems, vol-3, pp. 67-80, August 2012.

- [18] J. C. Morizio, M. Hoke, T. Kocak, C. Hughes, J. Perry, S. Madhavapeddi, M. H. Hood, G. L. H. Kondoh, T. Kumamoto, T. Okuda, H. Noda, M. Ishiwaki, T. Miki and M. Nakaya "A 14 bit 2.2 MS/s sigma delta ADC" IEEE Journal of solid state circuit, Vol-35, pp. 968-976, July 2000.

- [19] Sandner C, Clara M, Santner A, Hartig T, Kuttner F. A 6-bit 1.2-GS/s low power flash ADC in 0.13 μm digital CMOS. IEEE Journal of Solid-State Circuits. 2005; vol. 40, pp. 1499-1505. July 2005.

### **BIBLIOGRAPHY OF AUTHORS**

Deepak Prasad was born in Dhanbad (Jharkhand) India in 1990. He received his Bachelor degree in Electronics and Communication Engineering from RGPV Bhopal in 2012 and Master degree in Electronics and Instrumentation from The Burdwan University in 2015. He has completed his M Tech project work from CSIR-Central Institute of Mining & Fuel Research (CIMFR) Dhanbad on the topic of "Design strata deformation indicator for underground coal mines" under the guidance of Senior Scientist Dr. P. K. Mishra. He has qualified GATE 2013 and GATE 2015 successfully. Presently he is working as Junior Research Fellow in ISRO Project entitled "Design of ultra low power CMOS (Complementary Metal Oxide Semiconductor) temperature sensor for aerospace application". He is also pursuing PhD on the same topic under the guidance of Dr. Vijay Nath, Department of Electronics and Communication Engineering, Birla Institute of Technology, Mesra Ranchi, Jharkhand. His research area includes analog, digital, mixed CMOS VLSI circuits, low power VLSI circuits, ADC, DAC, PTAT circuits. His design is selected in Top 6 all India Cadence Design Contest-2016 organized by Cadence Company Ireland. He has around 8 publications in national and international conferences.

Dr. Vijay Nath received his bachelor's degree in Physics and master's degree in Electronics from DDU Gorakhpur University, India in 1998 and 2001. He received a PGDCN from MMM Engineering College Gorakhpur (Gold Medalist) in 1999. He received his Ph.D. in VLSI Design & Technology from Dr. RML Avadh University, Faizabad in association with CEERI- Pilani in 2008. He was a member of the faculty of the Department of Electronics, DDU Gorakhpur University, Gorakhpur (2002-2006). In 2006, he joined as a faculty member in the Department of Electronics and Communication Engineering, Birla Institute of Technology Mesra, Ranchi, India. Currently he is Professor In-charge of VLSI Design Lab & Embedded System Design Lab, Dept. of ECE, BIT Mesra, Ranchi. His research interests include analog, digital, mixed CMOS VLSI circuits, low power VLSI circuits, ADC, DAC, PTAT, CMOS bandgap voltage reference, piezoresistive pressure sensors, double ring capacitive pressure sensors, MEMS sensors, signal-processing circuits, ASICs, embedded systems designs, smart cardiac pacemaker, and early stage cancer detection. He has to his credit around 100 publications in international journals and conferences. He is a member of several reputed professional and academic bodies including IETE, ISVE, and IEEE.