# **FPGA-based Architecture of Direct Torque Control**

Azaza Maher, Echaieb Kamel, Mami Abdelkader

National School of Engineering of Tunis ENIT, Laboratory of System Analysis and Control LACS. Elmanar University Tunis, Tunisia

| Article Info                                                          | ABSTRACT                                                                                                                                                      |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article history:                                                      | This paper presents an optimized FPGA architecture of a DTC "direct torque                                                                                    |

| Received Jan 3, 2017                                                  | control" drive of an induction motor. The proposed architecture is based on<br>variable fixed point world size and the use ipcores in order to achieve higher |

| Revised Jan 20, 2017                                                  | sampling frequency which leads to reduce the electromagnetic torque and                                                                                       |

| Accepted Jan 27, 2017                                                 | flux ripples. The hardware implementation was experimentally validated, the results shows the effectiveness of the hardware DTC drive implementation          |

| Keywords:                                                             | by the minimization of the torque and flux ripple.                                                                                                            |

| Drug suitability<br>Hypertension<br>Profile matching<br>Interpolation |                                                                                                                                                               |

| incipolation                                                          | Copyright © 2017 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                       |

| Corresponding Author:                                                 |                                                                                                                                                               |

| Azaza Maher,<br>National School of Engineering of T                   | 'unis ENIT,                                                                                                                                                   |

Laboratory of System Analysis and Control LACS, Elmanar University Tunis, Tunisia Email: maher.azaza@gmail.com

#### **INTRODUCTION** 1.

Before the power electronics is introduced, induction motors were mainly used for applications with almost constant speed because of the unavailability of a variable frequency drive. The advancement of power electronics has solved this problem and extended the use of induction motors for variable speed applications, but due to the inherent linkage of flux and torque, the performance did not reaches that of the DC machine. Decades ago, the methodology field oriented control (FOC) of an induction motor was established which has opened a new horizon for induction motors applications. This methodology is based on the frames transforms (Concordia, Park, Park inverse), and the decoupling of control variables. Its major drawback is the complexity of the control algorithm which makes this solution a complex operation from implementation on an embedded target.

The direct torque control DTC (Direct Torque Control) has been proposed in 1986 by Takahashi [1], it allows the speed control through the direct control of the motor electromagnetic variables. This technique uses a simpler control structure based on estimators and hysteresis regulators, to control independently the stator flux and torque. The simplicity lies in limited vector operations and coordinates transformation, the absence of modulation operations (PWM, SVM) and the non-necessity of a position sensor.

Although its structure is simple, DTC requires a fast processor to perform electromagnetic torque and stator flux estimator computation. Different embedded solutions were investigated to achieve a high sampling frequency F<sub>s</sub>, such as DSP [2]-[4] where its F<sub>s</sub> can reach up to 20 kHz. However, this is not enough for the discrete hysteresis controller to reaches the same performance as analog operation, where torque and flux ripple output are limited within the hysteresis band.

Therefore, other solutions have been proposed in the literature, some studies [6], [7], [8] have used a combination of DSP and FPGA to reduce the computational load on DSP by distributing tasks to the FPGA. However, this combination of software and hardware solution increases the cost and complexity of

interfacing the circuit and is not a practical solution for commercial purposes. Other studies [9]-[11] have proposed hardware FPGA based implementation of the entire DTC algorithm where the VHDL code was generated using Xilinx system generator toolbox of Matlab, a significant amelioration of torque and flux ripple were found but the VHDL code was not optimized to achieve higher sampling frequency.

In this work, a novel FPGA implementation of DTC based on hysteresis controller is developed using variable fixed point world size and involving ip-cores of Xilinx to compute complex functions involved in DTC algorithm such as the square root and trigonometric functions. The performance of the proposed FPGA architecture is experimentally validated. A high sampling frequency is achieved showing a significant reduced torque and flux ripple

# 2. DTC ALGORITHM

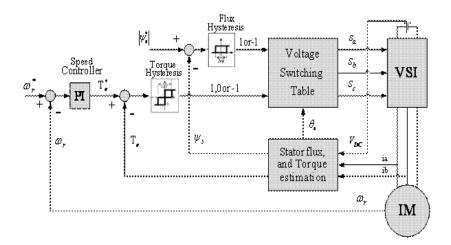

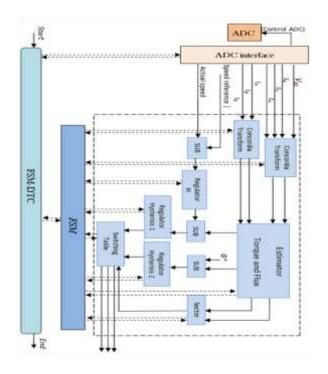

The DTC essentially consists of a torque control loop and a speed control loop, as shown in Figure 1. In this topology, the stator flux and electromagnetic torque are respectively controlled by the means of a 2 level and 3 level hysteresis regulators. The outputs of comparators and the sector number are used to index the switching table "look-up-table" in order to select the appropriate switching states of the inverter switches. In this loop, the most important sub-module that can guarantee satisfactory performance of the DTC is the estimator of the stator flux and torque [12], [13].

Figure 1. Modules of the DTC algorithm

The computation operations involved in the flux and torque estimator are described by the above equations:

•  $(\alpha,\beta)$  transform:

$$\begin{cases} I_{\alpha} = I_{a} \\ I_{\beta} = \frac{\sqrt{3}}{3} \left( I_{a} + 2I_{b} \right) \end{cases}$$

(1)

$$\begin{cases} V_{\alpha} = \frac{V_{dc}}{3} (2 S_{a} - S_{b} - S_{c}) \\ V_{\beta} = \frac{\sqrt{3}}{3} V_{dc} (S_{b} + S_{c}) \end{cases}$$

(2)

•*Stator flux in* ( $\alpha$ ,  $\beta$ ) *frame:*

$$\begin{cases} \varphi_{\alpha} = \varphi_{\alpha 0} + (V_{\alpha} - R_s I_{\alpha})T_s \\ \varphi_{\beta} = \varphi_{\beta 0} + (V_{\beta} - R_s I_{\beta})T_s \end{cases}$$

(3)

Where  $T_s$  is the sampling period (µs) and  $R_s$  is the stator resistance (ohms).

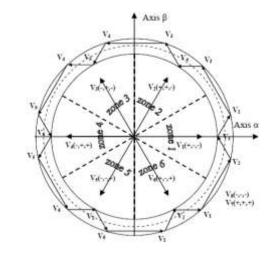

Neglecting the stator resistance, equations 13 and 14 implies that the tip of the stator vector will move in the direction of the applied voltage vector in a straight line as indicated in Figure 2. For controlling

the amplitude of the stator flux, the voltage vector plane is divided into six regions. Each of these sectors is  $60^{\circ}$  wide. In each region, two adjacent voltage vectors may be selected to increase or decrease the stator flux amplitude and give a minimum switching frequency [14]. The switching table is given by the Table 1:

| Table 1. Switching Table |    |                |                |                |                       |                |        |

|--------------------------|----|----------------|----------------|----------------|-----------------------|----------------|--------|

| φ                        | Т  | Zone 1         | Zone 2         | Zone 3         | Zone 4                | Zone 5         | Zone 6 |

| _                        | 1  | $V_2$          | $V_2$          | $V_4$          | V <sub>5</sub>        | $V_6$          | $V_1$  |

| Î                        | 0  | $V_7$          | $\mathbf{V}_0$ | $V_7$          | $\mathbf{V}_0$        | $V_7$          | $V_0$  |

| ÷                        | -1 | $V_6$          | $V_1$          | $V_2$          | $V_3$                 | $V_4$          | $V_5$  |

| 0                        | 1  | $V_3$          | $V_4$          | $V_5$          | $V_6$                 | $V_1$          | $V_2$  |

| Ĩ                        | 0  | $\mathbf{V}_0$ | $V_7$          | $\mathbf{V}_0$ | <b>V</b> <sub>7</sub> | $\mathbf{V}_0$ | $V_7$  |

| -0-                      | -1 | V.5            | $V_6$          | $V_1$          | $V_2$                 | $V_3$          | $V_4$  |

Figure 2. Selected stator voltage regrading the stator flux sector

The torque and flux hysteresis controllers select the appropriate voltage vectors. Table 1 indicate the six and eight voltage vectors switching strategies, in each region Te and  $\varphi$  are increasing or decreasing functions of time. When the torque is increasing or decreasing, the flux linkage can be increased or decreased by selecting alternatively one of the six non zero voltage vectors and one of the two zero voltage vectors. The torque and flux are increased or decreased by selecting only the six non zero voltage vectors. The torque is changed by reversing the movement of the stator flux vector at each state of the hysteresis controller output [17].

•Sector number of flux vector:

$$\phi_s = \arctan\left(\frac{\varphi_\alpha}{\varphi_\beta}\right) \tag{4}$$

•Torque and stator flux magnitude estimation:

$$\begin{cases} \varphi_{s} = \sqrt{\varphi_{\alpha}^{2} + \varphi_{\beta}^{2}} \\ T_{e} = \frac{3}{4} P(I_{\beta}\varphi_{\alpha} - I_{\alpha}\varphi_{\beta}) \end{cases}$$

(5)

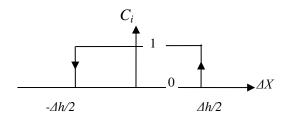

Where *P* is the pole's number of the induction motor,  $T_e$  is the electromagnetic torque (N.m) and  $\varphi_s$  is the stator flux magnitude (Wb). The flux 2-level hysteresis controller, as depicted in Figure 3, is described by the following equations:

Figure 3. 2-level hysterisis satates

$$\begin{cases} C_i = 1 & \text{if } \Delta X = (X_{ref} - X_{mes}) \ge \Delta h/2\\ C_i = 0 & \text{if } \Delta X = (X_{ref} - X_{mes}) \le \Delta h/2 \end{cases}$$

(6)

Where  $C_i$  is the control inverter control signal, and  $\Delta h$  is the hysteresis band. The torque 3-level hysteresis controller is described by the following equations:

$$\begin{cases} C_i = 1 \quad if \qquad \Delta X \le -\Delta h/2\\ C_i = 0 \quad if \qquad -\frac{\Delta h}{2} \le \Delta X \le \frac{\Delta h}{2}\\ C_i = -1 \quad if \qquad \Delta X \ge \Delta h/2 \end{cases}$$

(7)

# 3. FPGA BASED ARCHITECTURE

#### 3.1. Electromagnetic torque and stator flux estimator architecture

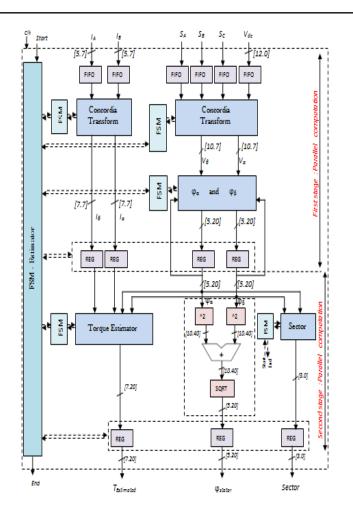

The major important module in DTC drive is the flux and torque estimator which involves different computational operations such as basic arithmetic binary addition, subtraction, multiplication. Other more complex calculation operations are also involved such as trigonometric functions and the square root computation, these operators add more complexity to the stage of implementation during which the performance and used FPGA resources are of major importance. In this work, the estimator is implemented in two pipelined stages as shown in Figure 4.

**D** 23

Figure 4. Architetcure of flux and torque estimator

The implementation of the estimator is performed using the two's complement fixed point format throughout the operations involved in the calculation algorithm with the exception of the operation of the square root. In this particular case, the numbers are represented in unsigned fixed point format as operand and the results are always positive.

The implementation of the estimator is performed using the two's complement fixed point format throughout the operations involved in the calculation algorithm with the exception of the operation of the square root. In this particular case, the numbers are represented in unsigned fixed point format as operand and the results are always positive.

Determining the number of bits allocated to a variable is one of the critical points in the implementation on FPGA. First, the use of an insufficient number of bits can reduce the precision and cause a calculation error, which can destabilize the overall system. On the other hand, may increase the over sizing of the hardware implementation surface such as the case when using floating pint format. In this work, the architecture is implemented using a variable fixed-point format depending on the mathematical operation to be performed.

The square root function and the "*arctg*" function involved in the stator flux magnitude and sector computation are performed by ipcores which are pre-optimized modules from timing and resources consumption point view. The estimator is implemented in two pipelined stages; In the first stage, the Concordia transform of stator currents and voltages as well as the stator flux in  $(\alpha, \beta)$  frame are performed in parallel computation. In the second stage, the estimated torque, the estimated stator flux magnitude, and the sector number computation are performed in parallel. The two sequential stages are synchronized using a number of registers. Different estimator operations are controlled by a local finite state machine FSM.

| IJRES                                                                      | ISSN: 2089-4864                                      |            | 25     |

|----------------------------------------------------------------------------|------------------------------------------------------|------------|--------|

| <b>3.2. FPGA Architecture of the DTC</b><br>The FPGA architecture of the D | TC algorithm is described in Figure 5. At the time t | tk, DTC co | ontrol |

sequencer is activated by the start signal at a high logic level, it triggers sequentially the digital analog conversion and the internal sequencer of the DTC. Initially Concordia transform and the PI controller are activated in parallel, these modules generate the values of I $\alpha$ , I $\beta$ , V $\alpha$  and V $\beta$  as well the torque reference value. After the estimator computation the sector position and the hysteresis controller are activated. Errors sates on the flux and torque are compared to the hysteresis band at the end of each computation cycle; the control pulses (S1, S2, S3) are generated and applied to the switches of the DC-AC inverter.

Figure 5. DTC architetcure

# 4. FPGA SYNTHESIS RESULTS

The FPGA synthesis results on Spartan-3E FPGA (XC3S500E-4FG320C) are presented in Table.2 and Table 3 as follow:

| Table 2. Ressources utilization summary |            |  |  |

|-----------------------------------------|------------|--|--|

| Resources utilization                   |            |  |  |

| Slices number                           | 970 (21%)  |  |  |

| LUTs Number                             | 1153 (13%) |  |  |

| Mult (18×18)                            | 2(10%)     |  |  |

| Table 3. FPGA computation performance                 |         |                |  |  |

|-------------------------------------------------------|---------|----------------|--|--|

| Module                                                | Latency | Execution Time |  |  |

| ADC                                                   | 120     | 2.4 µs         |  |  |

| Speed encoder                                         | 2       | 0.04 µs        |  |  |

| abc-αβ                                                | 4       | 0.08 µs        |  |  |

| Estimator : Teand Flux                                | 6       | 0.12 µs        |  |  |

| Sector position                                       | 4       | 0.08 µs        |  |  |

| Switching Table                                       | 4       | 0.08 µs        |  |  |

| Hysterisis                                            | 3       | 0.06 µs        |  |  |

| PI                                                    | 6       | 0.12µs         |  |  |

| $T_{DTC} = T_{\alpha\beta} + T_{Est} + T_{Secteur} +$ | 0.54 µs |                |  |  |

| $T_{total} = T_{DTC} + T_{AD}$                        | с.      | 3.22 µs        |  |  |

The implemented DTC algorithm is executed in 0.54  $\mu$ s, the total necessary time for the DTC is 3.22  $\mu$ s considering the analog to digital conversion.

# 5. EXPERIMENTAL RESULTS AND COMPARAISON

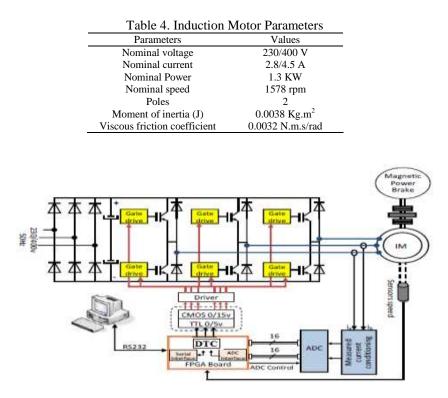

The experimental set up is described by the Figure 6. It consist of three main stages; power electronic stage (power supply, VSI), adaptation and conditioning (ADC, DAC, Amplifier, acquisition), the FPGA and the three phase induction motor with parameters are listed in Table 4.

Figure 6. Schematic of the experiment set up

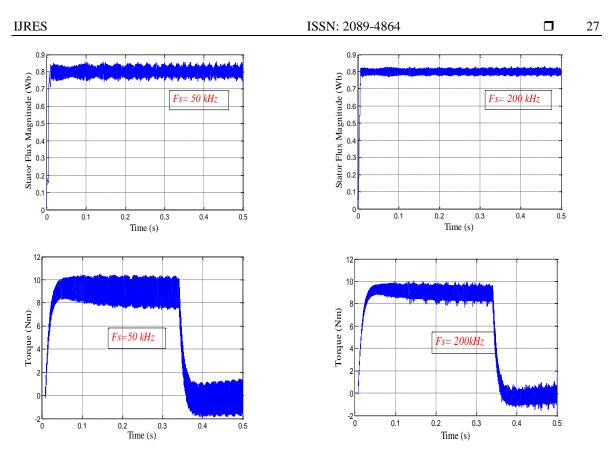

An experimental validation of the DTC implemented on FPGA is carried out to study the performance of the DTC FPGA-based components as well as the effectiveness of the developed hardware architecture that resulted in an execution time of  $3.22 \ \mu s$ . Figure 8 shows the experimental results of stator flux, the reference value is 0.8 Wb and the electromagnetic torque estimated for a sampling frequency of 50 kHz and a frequency of 200 kHz.

Figure 8. Stator Flux and electromagnetic torque estimated for a sampling frequency of 50 kHz and 200 kHz

Based on the experimental results of the DTC control performance is improved in terms torque ripple and stator flux when the sampling frequency increases. The torque and flux ripple achieved are respectively 12.5 % and 4.32 % showing the high performance of the proposed DTC architecture. Table 5 presents a comparaison of the proposed architecture to other works in the literature.

| Table 5. Comparaison Table |           |            |                                           |            |      |

|----------------------------|-----------|------------|-------------------------------------------|------------|------|

| Reference                  | Sampling  | DTC        | Plateform                                 | Ripple (%) |      |

| Reference                  | frequency | 510        | 1 Million Million                         | Torque     | Flux |

| Proposed                   | 200 kHz   | Hysterisis | FPGA                                      | 12.5       | 4.32 |

| [18]                       | 20 kHz    | Fuzzy      | FPGA Xilinx Virtex-V<br>xc5vfx70t-3ff1136 | 59.64      | 6.37 |

| [19]                       | 200 kHz   | Hysterisis | FPGA Altera<br>APEX20K200EFC484-2x        | 9.09       | 2    |

| [20]                       | (-)       | SVM        | FPGA Xilinx Spartan 3                     | 80%        | 10   |

# 6. CONCLUSION

This paper presented an FPGA implementation of a DTC drive. The DTC FPGA architecture was described where the estimator was highlighted. The estimator was implemented using a variable fixed point format in order to enhance its computation performance. In addition the hardware implementation was optimized to achieve higher sampling frequency leading to reduce the torque and flux ripple. The torque and stator flux ripple achieved are respectively 12.5% and 4.32% at a 200 kHz sampling frequency. The DTC performance is enhanced with an optimized FPGA resources utilization as well an execution time of 3.22  $\mu$ s considering the analog to digital conversion.

### REFERENCES

[1] Takahashi I, Noguchi T, "A New Quick-Response and High- Efficiency Control Strategy of an Induction Motor", *IEEE Transactions on Industry Applications*, 1986; 22; 827.1986.

- [2] Bose B. K, Szczesny P. M. "A microcomputer-based control and simulation of an advanced IPM synchronous machine drive system for electric vehicle propulsion", *Industrial Electronics, IEEE Transactions on.* 1988; 35; 547-559; 1988.

- [3] Lianbing L, "A high-performance direct torque control based on DSP in permanent magnet synchronous motor drive", *Intelligent Control and Automation, Proceedings of the 4th World Congress on*, 2002; 21622-1625.

- [4] Cruz S. M. A, "DSP implementation of the multiple reference frames theory for the diagnosis of stator faults in a DTC induction motor drive", *Energy Conversion, IEEE Transactions on*. 2005; 20; 329-335.

- [5] Riesgo T, Torroja Y, Dela Torre E, "Design methodologies based on hardware description languages," *IEEE Trans. Ind. Electron.* 1999; 46 (1); 3–12.

- [6] Jidin A, "Simple Dynamic Overmodulation Strategy for Fast Torque Control in DTC of Induction Machines with Constant Switching Frequency Controller", *Industry Applications Society Annual Meeting (IAS)*. 2010; 1-8.

- [7] Trimberger S. "A reprogrammable gate array and applications". Proc. IEEE. 1993;81; 1030–1041.

- [8] Monmasson E, Cirstea M. N, "FPGA Design Methodology for Industrial Control Systems: A Review", *Industrial Electronics, IEEE Transactions on.* 2007; 54;1824-1842.

- [9] Ferreira S, "Design and prototyping of direct torque control of induction motors in FPGAs", *Integrated Circuits and SystemsDesign, 2003. SBCCI 2003. Proceedings. 16th Symposium on*; 2003;105-110.

- [10] Riesgo T, Torroja Y, Dela Torre E, "Design methodologies based on hardware description languages", IEEE Trans. Ind. Electron. 1999; 46 (1); 3–12.

- [11] Dinu A, "FPGA neural controller for three phase sensorless induction motor drive systems", Ph.D. dissertation, De Montfort Univ., Leicester, U.K., 2000.

- [12] Chapuis Y.A, Blonde J. P, Braun F. "FPGA Implementation by Modular Design Reuse Mode to Optimize Hardware Architecture and Performance of AC Motor Controller Algorithm", Proc. EPE-PEMC Conf; 2004.

- [13] Charaabi L, Monmasson E, Slama-Belkhodja I, "Presentation of an efficient design methodology to develop IP-core functions for control systems: Application to the design of an antiwindup PI controller", *Proc. IEEE IECON*, Sevilla, Spain, Nov. 2002.

- [14] Monmasson E, Cirstea M, "FPGA Design Methodology for Industrial Control Systems A Review", IEEE Trans. Ind. Electron. 2007; 54(4);1824-1842.

- [15] Trimberger S, "A reprogrammable gate array and applications", Proc. IEEE, 1030–1041; Jul. 1993.

- [16] Jidin A, "An Optimized Switching Strategy for Quick Dynamic Torque Control in DTC-Hysteresis-Based Induction Machines", *Industrial Electronics, IEEE Transactions on*. 2011; 58; 3391-3400.

- [17] Jidin A, "Torque ripple minimization in DTC induction motor drive using constant frequency torque controller", *Electrical Machines and Systems (ICEMS)*, 919-924, 2010.

- [18] Soufien G, Abdellatif M, Mohamed M, "Design and Experimental Implementation of DTC of an Induction Machine Based on Fuzzy Logic Control on FPGA", *IEEE transactions on fuzzy systems*. 2015;23;99.

- [19] Sutikno T, Nik Idris NR, Jidin A, Cirstea MN, "An Improved FPGA Implementation of Direct Torque Control for Induction Machines", *IEEE Transactions on Industrial Informatics*. 2013; 9 (3); 1280 – 1290.

- [20] Rajendran R, Devarajan N, "FPGA Based Implementation of Space Vector Modulated Direct Torque Control for Induction Motor Drive" International Journal of Computer and Electrical Engineering. 2010; 2 (3); 589-594.