# Design and Implementation of 8x8 Multiplier using 4-2 Compressor and 5-2 Compressor

**K. Hari Kishore, K. Akhil, G. Viswanath, N. Pavan Kumar** Department of ECE in K L University Green fields-522502, AP, India

| Article Info                                                              | ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Article history:                                                          | In this paper, a 8x8 multiplier is realized by using 4-2 and 5-2 compressors.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Received Apr 24, 2016<br>Revised Aug 3, 2016<br>Accepted Aug 18, 2016     | Low-power high speed 4-2 compressors and 5-2 compressors are extensively<br>utilized for numerical realizations. Both the compressors circuits that is the<br>4-2 compressor circuit and 5-2 compressor circuit internally consist of the<br>logic gates i.e. the XOR and XNOR gates. 4-2 compressor circuit has been<br>designed uses a brand new partial-product reduction format that                                                                        |  |  |

| Keyword:                                                                  | consecutively reduces the utmost output new style of number needs less variety of MOSFET's compared to Wallace Tree Multipliers. The 4-2                                                                                                                                                                                                                                                                                                                        |  |  |

| 4-2 compressor<br>5-2 compressor<br>Dadda multiplier<br>Power consumption | compressor used is created from high-speed and consists of logic gates XOR<br>and XNOR gates and transmission gate primarily based electronic device.<br>The regular delay and switching energy also called as power-delay product<br>(PDP) is differentiated with the 5-2 compressor enforced with 4-2<br>Compressors and while not compressors, and is evidenced to own minimum<br>delay and PDP. Simulations are performed by mistreatment Xilinx ten.1 ISE. |  |  |

|                                                                           | Copyright © 2013 Institute of Advanced Engineering and Science.<br>All rights reserved.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

## Corresponding Author:

K. Akhil, Department of ECE in K L University Green fields-522502, AP, India. Email: kvruakhil2@gmail.com

## 1. INTRODUCTION

Multipliers square measure one in all the foremost important blocks in pc arithmetic and square measure usually utilized in totally different digital signal processors. The urge for this high speed multipliers are enormously growing in numerical computing applications, like special effects, scientific calculation, and digital processing of images etc. The rate of multiplication factor depends on how briskly the compressors can work and designer's square measure currently additional centered on the delay and power consumption level. The multiplier factor design involves a series of steps. Among them the creation of the partial product stage is the first stage, and second one is reduction of above stage and lastly the summation stage.

The reduction of the first stage is accountable for a large area of the entire time lag in the multiplication, energy and space. Mostly the compressors typically execute this stage as a result of they give to the reduction of the partial merchandise and in addition to this they give to scale back the essential way that is very keen in describing the performance of the circuit. Compressors square measure used for addition operation and that they contribute for reduced essential path delay that is very important in maintaining circuit's performance. This will be accomplished with usage of 3- a pair of Compressors (Full-Adders) and 4-2 Compressors. These compressors square measure internally manufactured from XOR-XNOR and electronic device modules and their improved style can contribute plenty towards the general system performance. In gift work, 4-2 mechanical device made of high-speed and low-power XOR gate and XNOR gate and transmission gate primarily based electronic device is used. A brand new technique of partial-product reduction victimization 4-2 Compressors in multipliers are projected supported pre-determined sequence of matrix heights to allow minimum variety of partial-product reduction stages, with reduces delay and PDP of multiplier factor and has lesser junction transistor count.

#### 2. 4-2 COMPRESSOR

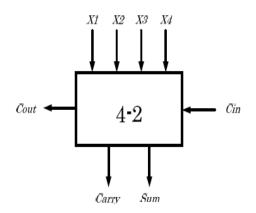

The compressor can be defined as device or a circuit which is for the most part utilized in multiplication in which a part of multipliers to reduce the operands .Generally a compressor of size M-N indicate that there are M bits that has to be given as inputs to the compressor and N indicates the result that is the output of the compressor. The 3-2 compressor is the most likely used compressor. The 3-2 compressor circuit indicates that there are 3 input bits that are to be added and finally 2 output bits is given to the next level. Similarly the working of a 4-2 compressor looks same as that of the two 3-2 compressors. The unique layout of 4-2 compressor device internally consists of two full adders, as appeared in figure. The unique layout of 4-2 compressor is accounted for in writing and these are overseeing by the fundamental mathematical statement as takes after: here are several encryption and decryption algorithms. An encryption algorithm involves transferring of message by adding cryptographic security. Encryption algorithms involve one or more keys which are similar to one user. This algorithms provides security to the data against the attackers when passing through the channel. Based on number of keys used the encryption algorithms are classified into two types, they are:

x1+x2+x3+x4+Cin=aggregate + 2.(Carry + Cout)

Figure 2.1. 4-2 Compressor

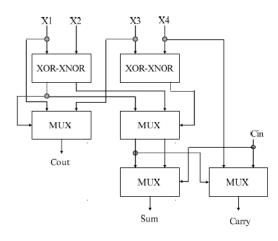

The regular execution of a 4-2 Compressor is expert by using two 3-2 compressors (FA) cells (Figure 3). Diverse outlines have been introduced in the writing for 4-2 Compressor. The improved outline of an exact4-2 Compressor in view of the supposed XOR-XNOR entryways; a XOR-XNOR door all the while creates the XOR gate and XNOR gate yield signals. The configuration comprises of 3 XOR gates and XNOR gates (indicated by XOR\*) doors, 1 XOR and two 2x1 Multiplexers. The basic way of the mentioned configuration has a postponement of 3 $\delta$ , where  $\Delta$  is the unitary deferral through any entryway in the outline.

Figure 2.2. 4-2 compressor XOR -XNOR module

## 3. 5-2 COMPRESSOR

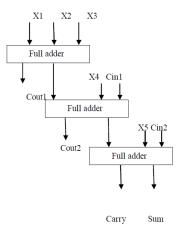

A 5-2 Compressor consists of 5 input bits ,denoted as x1, x2, x3, x4, x5 and two convey inputs Cin1 and Cin2 and produces 4 yields like Aggregate, Convey, Cout1 and Cout2. The data convey bits are the yields from the past square of compressor and the yield conveys are given to the progressive phase of compressor. This can be executed by utilizing three phases of full adders which are associated in arrangement as appeared in figure.

Figure 2.3. 5-2 Compressor

### **3.1. Multiplication**

In this area, the effect of utilizing the proposed compressors for duplication is researched. A quick (correct) multiplier is normally made out of three sections (or modules).

• Incomplete item era.

• A multiplier is made of Carry Save Adder (CSA) tree to decrease the fractional items' network to an expansion of just 2 inputs that is operands.

• A Carry Propagation Adder (CPA) for the final calculation of the parallel result.

In this configuration of a multiplier, the second part assumes a crucial part as far as deferral, force utilization and circuit multifaceted nature. The compressors are generally utilized to accelerate the CSA tree and diminishing energy dissemination, so to accomplish quick and low-control operation. The utilization of surmised compressors in the CSA tree of a multiplier results in an inexact multiplier.

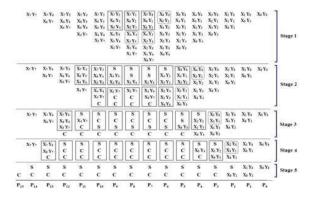

#### 3.2. Dadda Multiplier

Dadda proposed a calculation with foreordained succession of lattice (stage) statures for NxN multipliers to have decreased number of diminishment stages. It is created by working once again from two line stage. The stature of every middle of the road stage is constrained to floor estimation of 1.5 times the tallness of the successor stage [11]. i.e., Stature of stage i = (3/2) \* Tallness of stage i+1. At that point arrangement of stage statures are 2, 3, 4, 6, 9, 13...

Figure 3.1. Dadda multiplier

Design and Implementation of 8x8 Multiplier using 4-2 Compressor and 5-2 Compressor (K. Akhil)

## 4. 4-2 AND 5-2 COMPRESSOR USING MULTIPLICATION

## 4.1. Dadda Multiplier with 4-2 Compressor

Dadda proposed a calculation with foreordained grouping of network (stage) statures for NxN multipliers to have decreased number of diminishment stages. It is produced by working again from two column stage. The tallness of every middle of the road stage is constrained to floor estimation of 1.5 times the stature of the successor stage. i.e., Stature of stage i = (3/2) \* Tallness of stage i+1. At that point arrangement of stage statures are 2, 3, 4, 6, 9, 13...

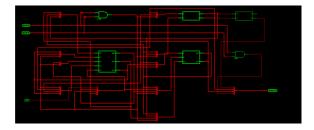

Figure 4.1. Dadda multiplier with 4-2 compressor

Figure 4.2. Dadda Multiplier with 5-2 compressor

## 5. TABULATION

| T 11 7 1   | D 1            | 1 .           |             |

|------------|----------------|---------------|-------------|

| Table 5 1  | Power value    | s when iising | compressors |

| 1 4010 5.1 | . I Ower vulue | s when using  | compressors |

| Multiplier               | Power      |

|--------------------------|------------|

| 4-2compressor multiplier | 0.056watts |

| 5-2 compressor           | 0.040W     |

## 6. **RESULTS**

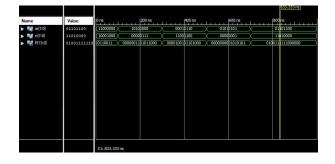

Figure 6.1. In the above figure m[7:0] and n[7:0] are the inputs and P[15:0] is the product. The result is shown by 4-2 compressor

Figure 6.2. In the above figure m[7:0] and n[7:0] are the inputs and P[15:0] is the product. The result is shown by 5-2 compressor

## 7. CONCLUSION

A novel transistorized 8x8 multiplier has been exhibited for fast execution, which utilizes 4-2 and 5-2 compressors which are designed with XOR XNOR and full adders of rapid and low power and Multiplexer. We have concluded that 5-2 compressor technique is better when compared to 4-2 compressor and without compressor technique while implementing dadda algorithm for multiplication. The Power consumed while using 5-2 compressor is less when compared to 4-2 compressor. The values are specified in the above table. This compressor technique can be preferred for low power and complex electronic circuits. The 8x8 multiplier shows ideal speed execution against essential Dadda multiplier actualized with and without the Compressor techniques and power consumption values are specified in the above table. This proposed multiplier uses a decrease group with foreordained stage statures for having snappy results and further least power delay item (PDP). This proposed lessening arrangement can likewise be connected to higher request NxN multipliers for rapid results.

#### REFERENCES

- [1] Sanjeev Kumar, *Manoj Kumar 4-2 Compressor design with New XOR-XNOR Module*, 4th International Conference on Advanced Computing and Communication technologies, pp. 106-111, 2014.

- [2] Z. Wang, G. A. Jullien, and W. C. Miller, A new design technique for column compression multipliers, *IEEE Trans. Computers*, vol.44, pp. 962-970. Aug 1995.

- [3] Harikishore Kakarla, Madhavi Latha M and Habibulla Khan, "Transition Optimization in Fault Free Memory Application Using Bus-Align Mode", *European Journal of Scientific Research (EJSR-Scopus)*, Vol.112, No.2, pp.237-245, ISSN: 1450-216x135/1450-202x, October 2013 (IF-0.736).

- [4] R. Zimmermann and W. Fichtner, —Low-power logic styles: CMOS versus pass-transistor logic, *IEEE Journal of Solid–State Circuits*, vol.32, pp.1079-1090, July 1997.

- [5] Harikishore. Kakarla, Madhavi Latha.M and Habibulla Khan, "Self Correcting Memory Design For Fault Free Coding In Progressive Data Streaming Application", *International Journal of VLSI design & Communication Systems (VLSICS) Vol.3*, No.1, ISSN: 0976 - 1357 (Online); 0976 - 1527 (print), February 2012.

- [6] M. Zhang, J. Gu, and C. H. Chang, —A novel hybrid pass logic with static CMOS output drive full-adder cell, in Proc. IEEE Int. Symp. Circuits Syst., pp.317 -320, May 2003.

- [7] M. Shams, T. K. Darwish, and M. A. Bayoumi, —Performance analysis of low-power 1-bit CMOS full adder cells, *IEEE Transactions on VLSI Systems*, vol. 10, pp. 20–29, Feb. 2002.

- S.F. Hsiao, M.R. Jiang, J.S. Yeh, —Design of high low power 3-2 counter and 4-2 compressor for fast multipliers, Electronic Letters, Vol. 34, No. 4, pp. 341-343, 1998

- [9] A. Weinberger, -4:2 Carry-Save Adder Module, IBM Technical Disclosure. Bulletin, Vol.23, January 1981.

- [10] S. Veeramachaneni, K. M. Krishna, L. Avinash, S. R. Puppala, and M. Srinivas, —Novel architectures for highspeed and low-power 3-2, 4-2 and 5-2 compressors, in VLSI Design. Held jointly with 6th International Conference on Embedded Systems, 20th Intern. Conference on, pp.324–329, Jan. 2007.

- [11] 4-2 Compressor Design with New XOR-XNOR Module in international journal of electronics and computer science engineering.

- [12] Korraprolu Brahma Reddy, K Hari Kishore, "A Mixed Approach for Power Dissipation Reduction in Nanometer CMOS VLSI circuits", *International Journal of Applied Engineering Research (IJAER-Scopus)*, ISSN 0973-4562 Volume 9, Number 18, pp. 5141-5148, July 2014.

- [13] Jorge Tonfat, Ricardo Reis, "Low Power 3-2 and 4-2 Adder Compressors Implemented Using ASTRAN", IEEE Third Latin American Symposium on Circuits and Systems (LASCAS), Feb. 29, 2012-March 2, 2012.

- [14] Harikishore. Kakarla, Madhavi Latha.M and Habibulla Khan, "Optimal Self Correcting Fault Free Error Coding Technique In Memory Operation", *International Journal Of Computer Science and Information Technology* (*IJCSIT*), Vol.3, No.3, ISSN: 0975-3826(online); 0975-4660 (Print), June 2011.